# Radio, RF and Video Applications

# Radio, RF and Video Applications

All products are sold on Motorola's Terms & Conditions of Supply. In ordering a product covered by this document the Customer agrees to be bound by those Terms & Conditions and nothing contained in this document constitutes or forms part of a contract (with the exception of the contents of this Notice). A copy of Motorola's Terms & Conditions of Supply is available on request.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and was registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

The Customer should ensure that it has the most up to date version of the document by contacting its local Motorola office. This document supersedes any earlier documentation relating to the products referred to herein. The information contained in this document is current at the date of publication. It may subsequently be updated, revised or withdrawn.

Includes literature available at June 1994

All trademarks recognized.

© MOTOROLA INC. All Rights Reserved First Edition DL413/D, 1991 DL413/D Rev. 1, 1994

Printed in Great Britain by Tavistock Press (Bedford) Ltd. 5000 9/94

#### **Preface**

This compilation of Application Notes, Engineering Bulletins, Design Concepts, etc. was originally published by the European Literature Centre of Motorola Ltd. in Milton Keynes, England, and has subsequently gained worldwide acceptance.

Because of the worldwide popularity of the Application Manuals Series it is important for the reader to take note of the following:

The various Application Notes, Engineering Bulletins, Design Concepts, etc. which are included were developed at Design Centres strategically located throughout the global community and many were originally written to support a local need. Whilst the basic concepts of each of the publications included may have broad global applicability, specific Motorola semiconductor parts may be referred to that are currently available for limited distribution in a specific region and may only be supported by the country of origin of the document in which it is referenced.

Also included in the series for completeness and historical significance are documents that may no longer be available individually because obsolete devices are referenced or perhaps, simply, the original document is out of print. Such items are marked in the Table of Contents, Cross Reference, Abstracts and on the first page of the document with the letters 'HI' to indicate that these documents are included for Historical Information only.

All the Application Notes, Engineering Bulletins, Design Concepts, etc. are included to enhance the user's knowledge and understanding of Motorola's products. However, before attempting to design-in a device referenced in this Series, the user should contact the local Motorola supplier or sales office to confirm product availability and if application support is available.

Thank you.

#### Other books in this series include:

DL408/D Rev. 1 8-bit MCU Applications Manual

DL409/D Rev. 1 16/32-bit Applications Manual

DL410/D Rev. 1 Power Applications Manual

DL411/D Rev. 1 Communications Applications

DL412/D Rev. 1 Industrial Control Applications

DL414/D FET Applications Manual

#### Contents

| D' O                 | P. Constant                                                                          | page |

|----------------------|--------------------------------------------------------------------------------------|------|

|                      | ss Reference                                                                         |      |

|                      |                                                                                      | 13   |

| Application<br>AN438 | s Documents  300W, 88-108MHz Amplifier Using the TP1940 MOSFETs Push-Pull Transistor | 21   |

| AN438<br>AN448       |                                                                                      |      |

| AN448<br>AN460       | "FLOF" Teletext using M6805 Microcontrollers                                         |      |

| AN460<br>AN463       | 68HC05K0 Infra-Red Remote Control                                                    |      |

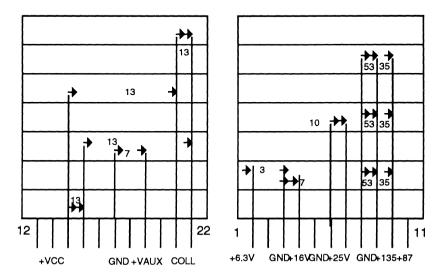

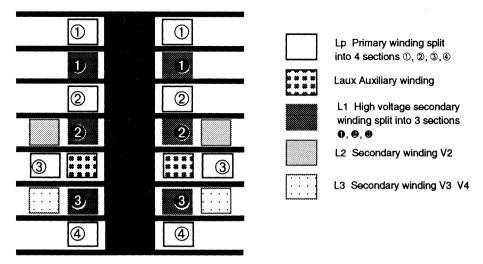

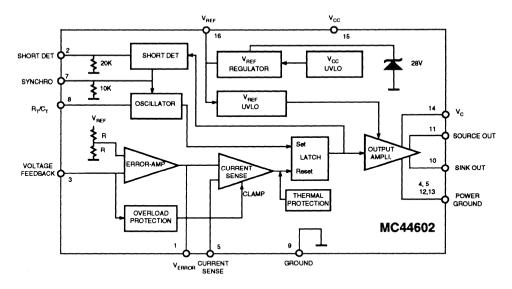

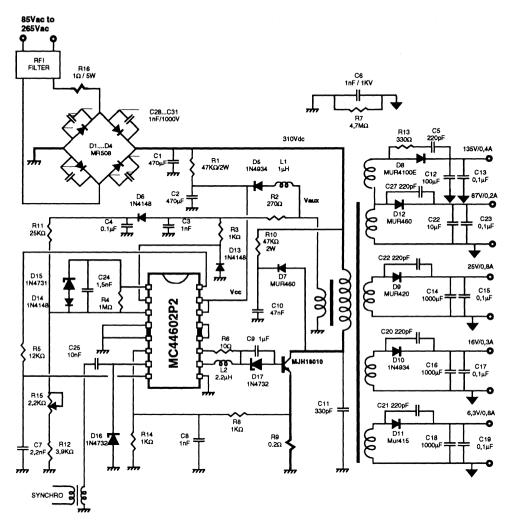

| AN479                | Universal Input Voltage Range Power Supply for High Resolution Monitors              | 101  |

| AN479                | with Multi-Sync Capability                                                           | 113  |

| <b>AN</b> 749        | Broadband Transformers and Broadband Combining Techniques for RF                     |      |

| AN756                | Crystal Switching Methods for MC12060/MC12061 Oscillators                            | 135  |

| AN790                | Thermal Rating of RF Power Transistors                                               |      |

| AN879                | Monomax: Application of the MC13001 Monochrome Television Integrated Circuit         | 147  |

| AN925                | UHF Preamplifier Centers on Budget Dual-Gate GaAs FET                                | 159  |

| AN932                | Application of the MC1377 Colour Encoder                                             | 165  |

| AN1019               | Decoding Using the TDA3330, with Emphasis on Cable In/Cable Out Operation            | 177  |

| AN1020               | A High-Performance Video Amplifier for High Resolution CRT Applications              | 185  |

| AN1021               | A Hybrid Video Amplifier for High Resolution CRT Applications                        | 189  |

| AN1022               | Mechanical and Thermal Considerations in Using RF Linear Hybrid Amplifiers           | 193  |

| AN1025               | Reliability Considerations in Design and Use of RF Integrated Circuits               | 197  |

| AN1027               | Reliability/Performance Aspects of CATV Amplifier Design                             | 205  |

| AN1028               | 35/50 Watt Broadband (160-240MHz) Push-Pull TV Amplifier Band III                    | 213  |

| AN1029               | TV Transposers Band IV and V Po = 0.5W/1.0W                                          | 221  |

| AN1030               | 1W/2W Broadband TV Amplifier Band IV and V                                           | 229  |

| AN1032               | How Load VSWR Affects Non-Linear Circuits                                            | 237  |

| AN1033               | Match Impedances in Microwave Amplifiers                                             | 241  |

| AN1034               | Three Balun Designs for Push-Pull Amplifiers                                         | 247  |

| AN1037               | Solid State Power Amplifier, 300W FM, 88-108MHz                                      | 253  |

| AN1039               | 470-860 MHz Broadband Amplifier 5W                                                   | 257  |

| AN1040               | Mounting Considerations for Power Semiconductors                                     | 263  |

| AN1041               | Mounting Procedures for Very High Power RF Transistors                               | 283  |

| AN1044               | The MC1378 — A Monolithic Composite Video Synchronizer                               | 285  |

| AN1047               | Electrical Characteristics of the CR2424 and CR2425 CRT Driver Hybrid Amplifiers     | 299  |

| AN1061               | Reflecting on Transmission Line Effects                                              | 303  |

| AN1080               | External-Sync Power Supply with Universal Input Voltage Range for Monitors           | 315  |

| AN1092               | Driving High Capacitance DRAMs in an ECL System                                      | 335  |

| AN1106               | Considerations in Using the MHW801 and MHW851 Series RF Power Modules                | 339  |

| AN1107               | Understanding RF Data Sheet Parameters                                               | 343  |

| AN1122               | Running the MC44802A PLL Circuit                                                     | 359  |

| AN1207               | The MC145170 in Basic HF and VHF Oscillators                                         | 371  |

| AN1306               | Thermal Distortion in Video Amplifiers                                               | 377  |

| AN1401               | Using SPICE to Analyze the Effects of Board Layout on System Skew when               |      |

| 4 5 1 4 4 6 7        | Designing with the MC10/100H640 Family of Clock Drivers                              |      |

| AN1402               | MC10/100H00 Translator Family I/O SPICE Modelling Kit                                |      |

| AN1404               | ECLinPS Circuit Performance at Non-Standard VIH Levels                               |      |

| AN1405               | ECL Clock Distribution Techniques                                                    | 419  |

#### Contents (continued)

| EB27A             | Get 300 Watts PEP Linear Across 2 to 30MHz from this Push-Pull Amplifier       | 427 |

|-------------------|--------------------------------------------------------------------------------|-----|

| EB29              | The Common Emitter TO-39 and its Advantages                                    | 431 |

| EB59              | Predict Frequency Accuracy for MC12060 and MC12061 Crystal Oscillator Circuits | 433 |

| EB77              | A 60 Watt 225-400MHz Amplifier - 2N6439                                        | 437 |

| EB89              | A 1 Watt, 2.3GHz Amplifier                                                     | 441 |

| EB90              | Low-Cost VHF Amplifier Has Broadband Performance                               | 445 |

| EB93              | 60 Watt VHF Amplifier Uses Splitting/Combining Techniques                      | 451 |

| EB107             | Mounting Considerations for Motorola RF Power Modules                          | 457 |

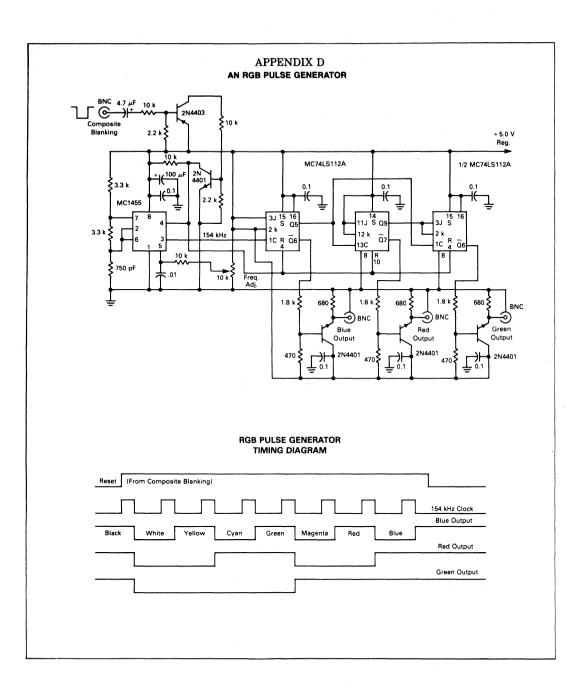

| EB411             | A Digital Video Prototyping System                                             | 461 |

| <b>Additional</b> | Information                                                                    | 471 |

# **Device Cross Reference**

#### **Device Cross Reference**

This quick-reference list indicates where specific components are featured in applications documents reproduced in this Manual.

| 2N6439           | EB77            | MC44250   | FR411  |

|------------------|-----------------|-----------|--------|

| CA2820           |                 | MC44602P2 |        |

| CR2424           | -               | MC44802A  |        |

| 0112424          |                 | MC145170  |        |

|                  | 1               | MHW612    |        |

| CR2425           |                 | MHW613    |        |

| 0112423          |                 | MHW709    |        |

| LT1001           |                 | MHW710    |        |

| LT1817           |                 | MHW720    |        |

| LT1829           |                 | MHW801    |        |

| LT5839           |                 | MHW808    |        |

| MC10E111         |                 | MHW820    |        |

| MC10E111         |                 | MHW851    |        |

| MC10E211MC10H60x |                 | MJE18004  |        |

|                  | · · · · · · · - |           |        |

| MC10H641         |                 | MJH18010  |        |

| MC10H64x         |                 | MOC8102   |        |

| MC10H660         |                 | MRF141G   |        |

| MC68HC05B6       |                 | MRF151G   |        |

| MC68HC05E0       |                 | MRF153    |        |

| MC68HC05K0       |                 | MRF154    |        |

| MC68HC05T7       | -               | MRF155    |        |

| MC68HC11E9       | . –             | MRF175G   |        |

| MC100E111        | -               | MRF176G   |        |

| MC100E211        |                 | MRF227    |        |

| MC100H60x        |                 | MRF260    |        |

| MC100H641        |                 | MRF262    |        |

| MC100H64x        |                 | MRF264    | EB93   |

| MC100H660        | AN1092          | MRF422    | EB27A  |

| MC1377           | AN932           | MRF430    | AN1041 |

|                  | AN1044          | MRF966    | AN925  |

| MC1378           | AN1044          | MRF2001   | EB89   |

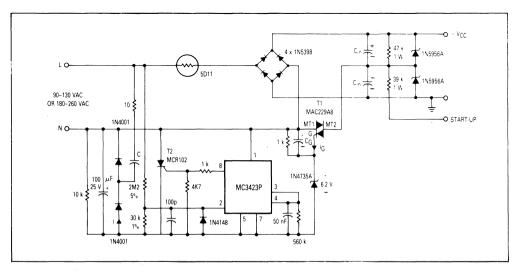

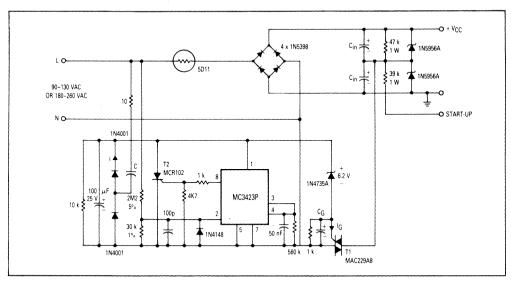

| MC1658           | AN1207          | MTP4N90   | AN1080 |

| MC1723           | EB27A           | TDA3301   | AN1044 |

| MC3423           | AN1080          | TDA3330   | AN1019 |

| MC12060          | AN756           | TP1940    | AN438  |

|                  | EB59            | TP9383    | AN1037 |

| MC12061          | AN756           | TPV375    | AN1028 |

|                  | EB59            | TPV593    | AN1039 |

| MC13001          | AN879           | TPV596    | AN1029 |

| MC14576          | EB411           | TPV597    | AN1030 |

| MC44011          | EB411           | UC3842A   |        |

| MC44200          | EB411           | UC3843A   |        |

|                  |                 |           |        |

## Abstracts of Applications Documents

#### **Abstracts**

#### AN438 300W, 88–108MHz Amplifier Using the TP1940 MOSFETs Push-Pull Transistor

Provides the design of an efficient 300W amplifier with high power gain, compact physical layout and operation on a 50V power supply. It uses the TP1940, a high power, high gain, broadband push-pull Power MOS-FET with low Reverse Transfer Capacitance. Includes circuit, parts list. PCB artwork and component layout.

#### AN448 "FLOF" Teletext using M6805 Microcontrollers

The "-T" members of Motorola's M68HC05 MCU family provide a cost-effective method of adding On Screen Display (OSD) to TVs and VCRs. This note describes an example of Full Level One Feature (FLOF) Teletext control software written for the MC68HC05T7 to control type 5243 Teletext chips. Around 3K bytes of ROM are used, allowing the code to fit with tuning, OSD and stereo functions into the 7.9K bytes of the MC68HC05T7. The example software includes the Spanish implementation of Packet 26; Packet 26 allows for the substitution of specific characters for a particular country.

#### AN460 An RDS Decoder Using the MC68HC05E0

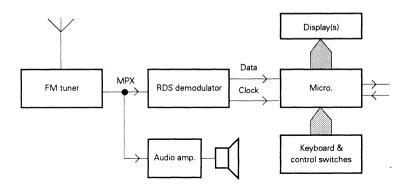

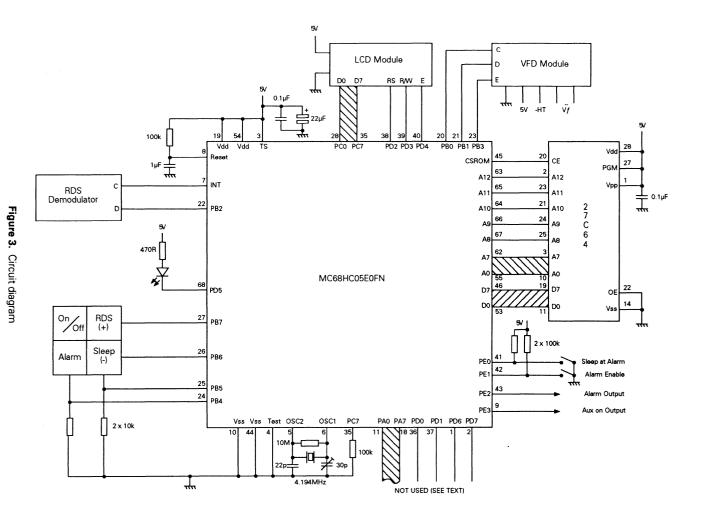

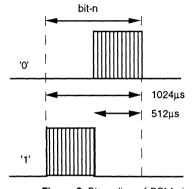

The Radio Data System (RDS) adds digital data capability to VHF FM transmissions on band II (87.5 to 108MHz). The system is in use in the UK and in several other European countries, and it is intended that it will be adopted eventually by most of Western Europe; it is defined by EBU Technical Document 3244. Information is transmitted in groups of four 26-bit blocks on a supressed 57kHz sub-carrier. This note describes an MC68HC05E0-based clock/radio application; it includes a complete software listing.

#### AN463 68HC05K0 Infra-Red Remote Control

In addition to the same CPU and registers as other members of the M68HC05 family the MC68HC05K0 has a 15-stage multi-function timer and 10 bidirectional I/O lines. A mask option is available for software programmable pull-downs on all the I/O pins; 4 of the pins are capable of generating interrupts. It is ideally suited for remote-control keyboard applications because the pull-downs and the interrupt drivers on the port pins allow keyboards to be built without any external components except the keys themselves. This application makes use of many of the on-chip features to control a TV infra-red remote control.

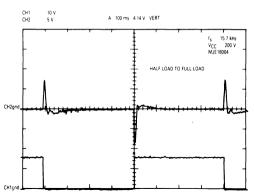

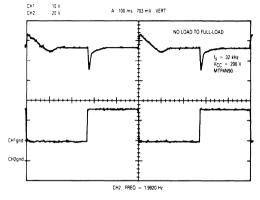

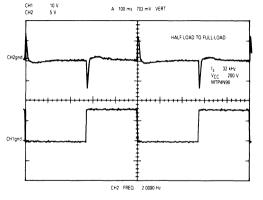

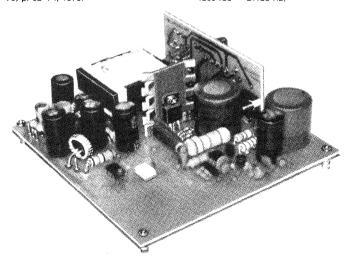

#### AN479 Universal Input Voltage Range Power Supply for High Resolution Monitors with Multi-Sync Capability

This note describes an easy-to-build, high performance, low cost 100W flyback power supply, able to work on any mains supply from 85Vac to 265Vac, and from 40Hz to 100Hz. It is automatically synchronised to the horizontal scanning frequency for minimum screen

interference on a multi-sync colour monitor. It uses a low cost MC44602P2 current mode controller – designed specifically for driving high voltage bipolar transistors – with an MJH18010 switchmode power transistor.

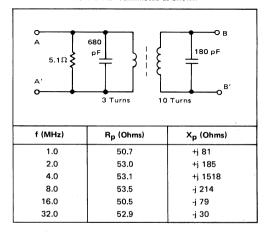

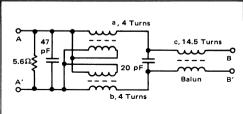

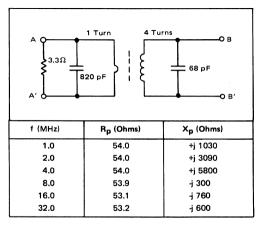

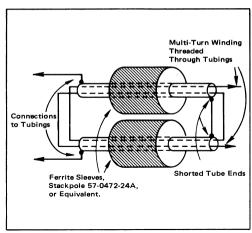

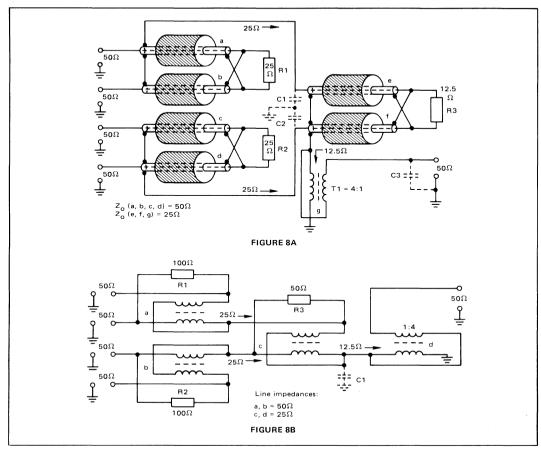

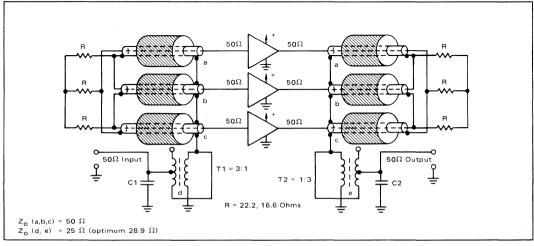

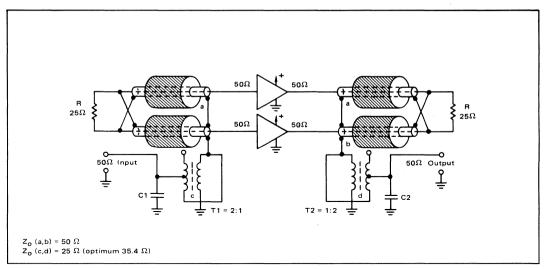

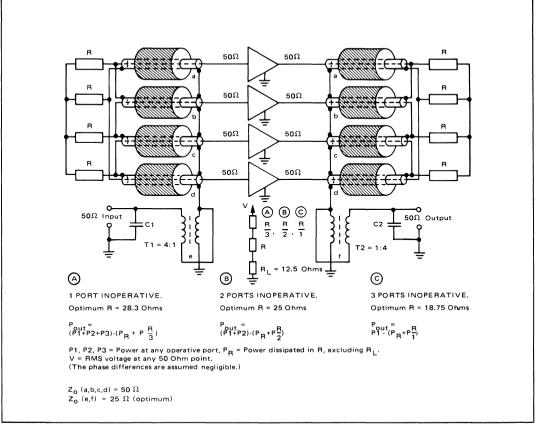

#### AN749 Broadband Transformers and Broadband Combining Techniques for RF

This application note provides a number of practical examples of broadband transformers for RF applications. It includes detailed design formulae and performance data, and discusses power combining techniques that are useful in designing high power RF amplifiers.

#### AN756 Crystal Switching Methods for MC12060/ MC12061 Oscillators

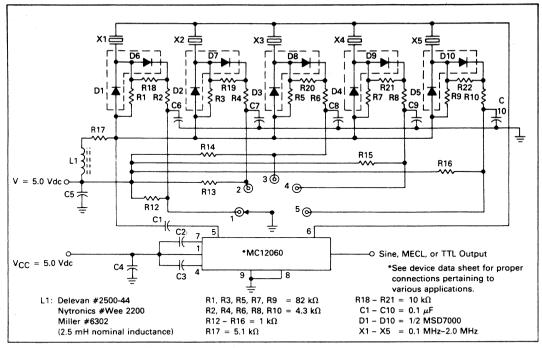

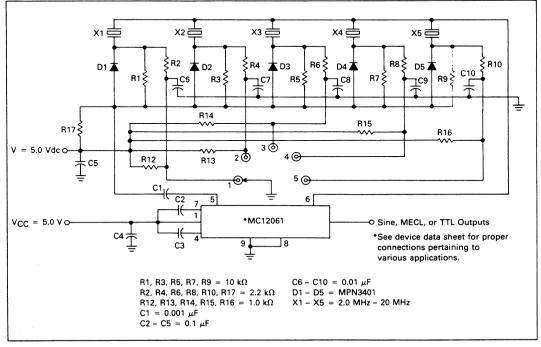

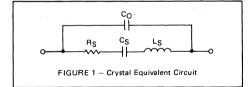

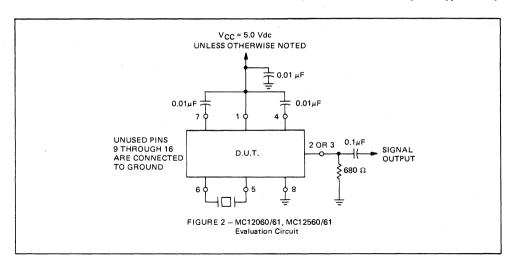

This report discusses methods of using diodes to select series resonant crystals electronically. Circuit designs suitable for use with crystal frequencies from 100kHz to 20MHz are developed, with emphasis on minimizing frequency pulling. Although developed for use with the MC12060 and MC12061 integrated circuit crystal oscillators, the techniques will generally be useful in any application where it is necessary to select electronically one of a group of crystals with minimum disturbance to the series resonant frequency of the selected crystal.

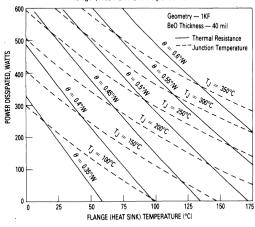

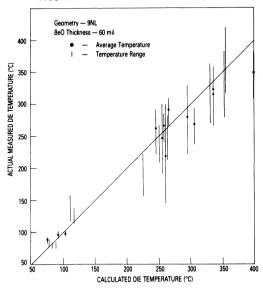

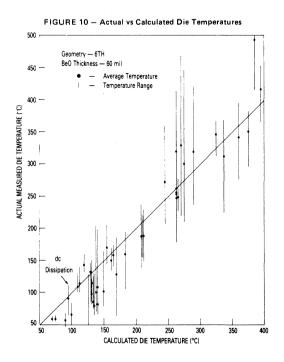

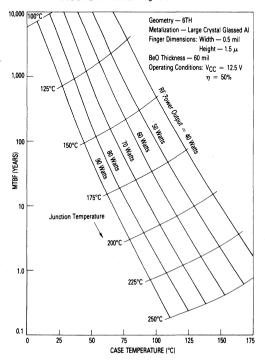

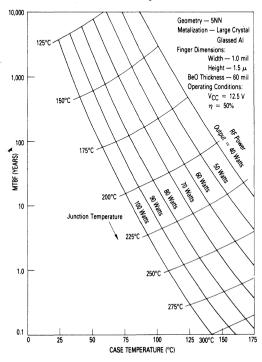

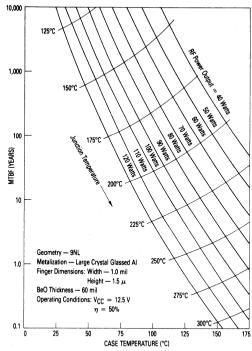

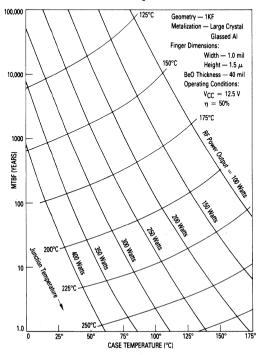

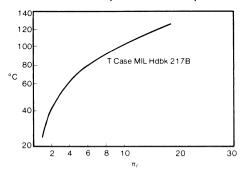

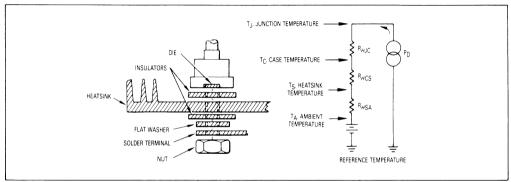

#### AN790 Thermal Rating of RF Power Transistors

Reliability is of primary concern to most transistor users. The degree of reliability achieved in practice is controlled by the device user because he determines environmental conditions and the stress levels applied. Knowledge of the basic physical properties of the materials, and the methods used to calculate thermal resistance, will assist the user in transistor selection and equipment design. This note clarifies and corrects some long-standing industry-wide assumptions about thermal resistance and high temperature derating.

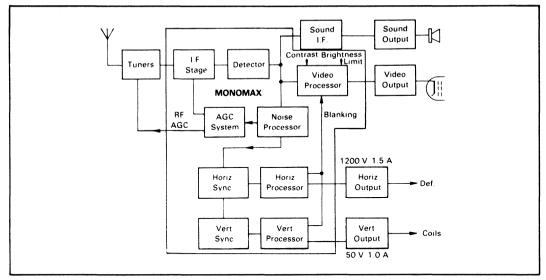

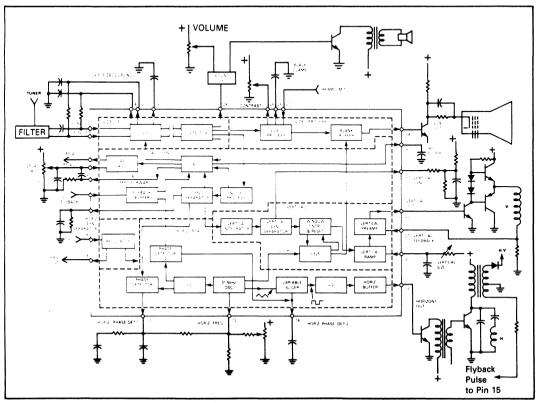

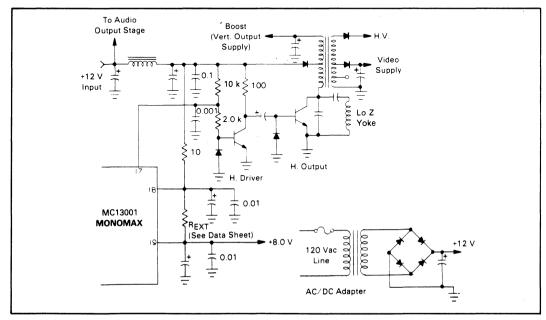

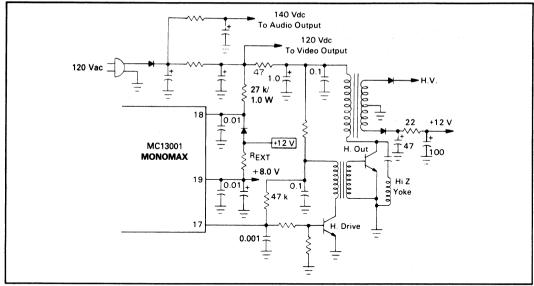

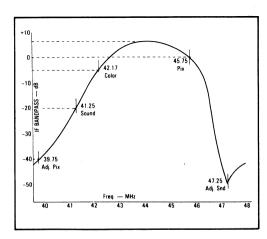

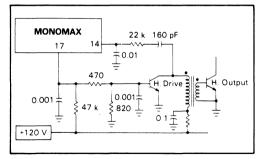

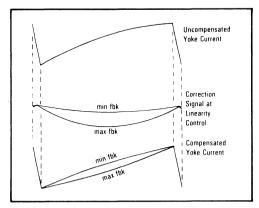

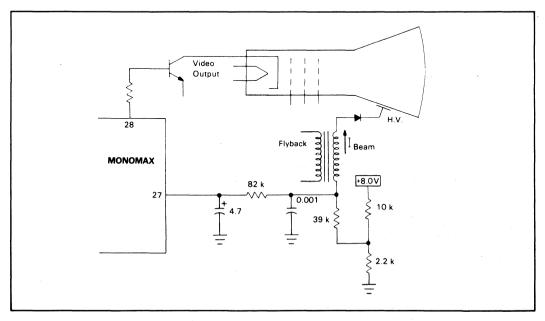

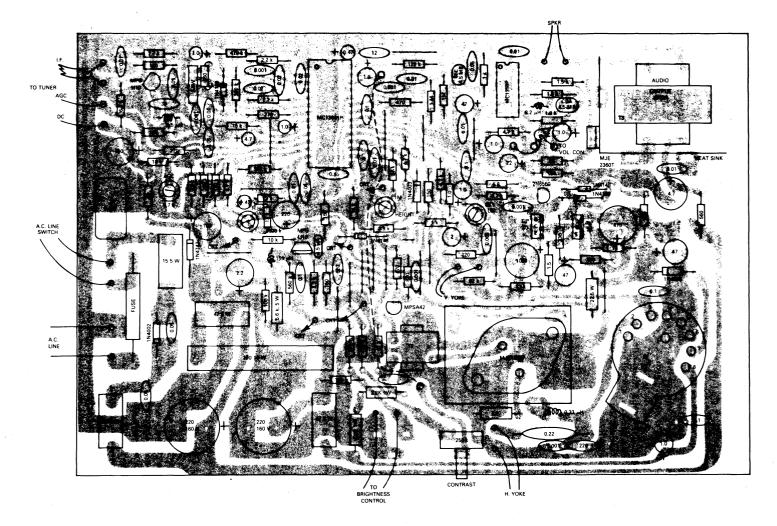

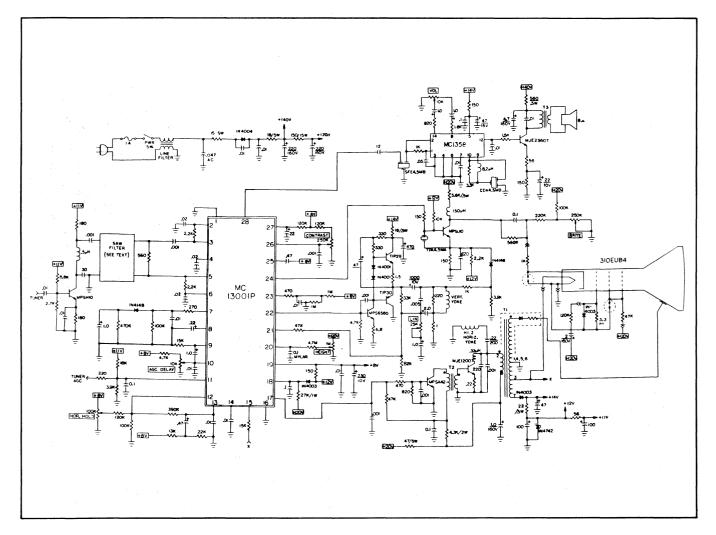

#### AN879 Monomax: Application of the MC13001 Monochrome Television Integrated Circuit

This application note presents a complete 12" black and white line-operated television receiver including artwork for the printed circuit board. It is intended to provide a good starting point for the first-time user. Some of the most common pitfalls are overcome and the significance of component selections and locations are discussed.

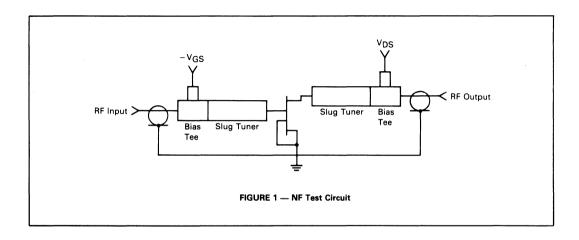

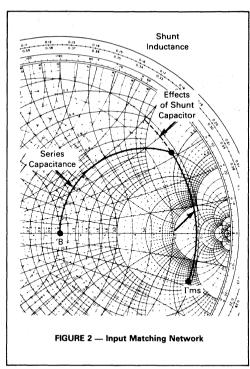

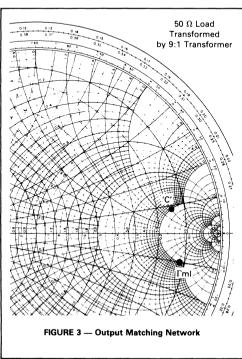

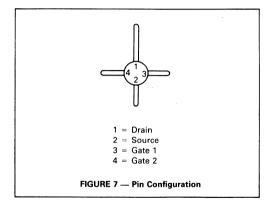

#### AN925 UHF Preamplifier Centers on Budget Dual-Gate GaAs FET

The signal-to-noise ratio of a communications system can be improved by increasing the power of the transmitter, increasing the gain of the antenna, or improving the sensitivity of the receiver. A low-noise preamplifier is an economical solution for receiver enhancement and this note describes the design, construction and performance of a 400-512MHz preamplifier using Motorola's dual-gate GaAs FET.

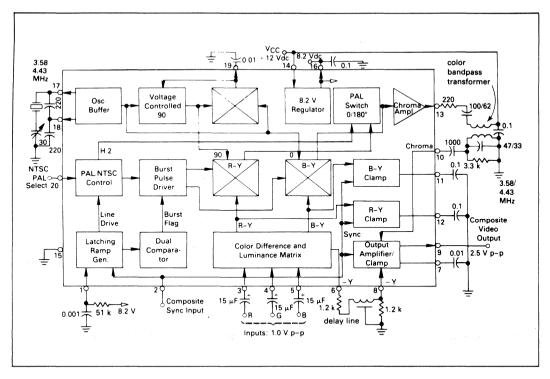

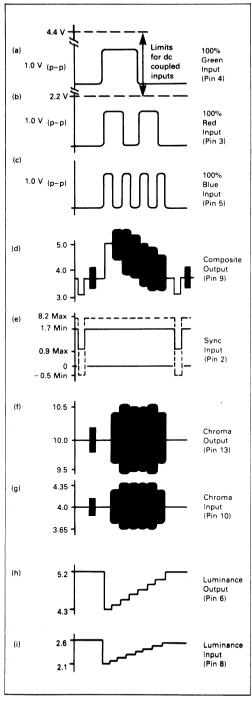

#### AN932 Application of the MC1377 Colour Encoder

The MC1377 is and economical, high quality, RGB encoder for NTSC or PAL applications. It accepts RGB and composite sync inputs, and delivers a 1V p–p composite NTSC or PAL video output into a 75 $\Omega$  load. It can provide its own colour oscillator and burst gating, or it can easily be driven from external sources. Performance virtually equal to high-cost studio equipment is possible with common colour receiver components.

#### AN1019 Decoding Using the TDA3330, with Emphasis on Cable In/Cable Out Operation

The TDA3330 is a Composite Video to RGB Colour Decoder originally intended for PAL and NTSC colour TV receivers and monitors – so its data sheet concentrates on picture tube drive. This practical application note supplements the data sheet by providing circuits for video cable drive as used in video processing, frame store and other specialized applications, and expands on TDA3330 functional details. Includes PCB artwork and layout of an evaluation board.

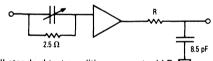

#### AN1020 A High-Performance Video Amplifier for High Resolution CRT Applications

This note describes a state-of-the-art video amplifier making use of the superior performance characteristics of Motorola CRT driver transistors. In particular, it shows the high speed obtainable with low DC power consumption. The circuit is insensitive to load variations and interconnect methods.

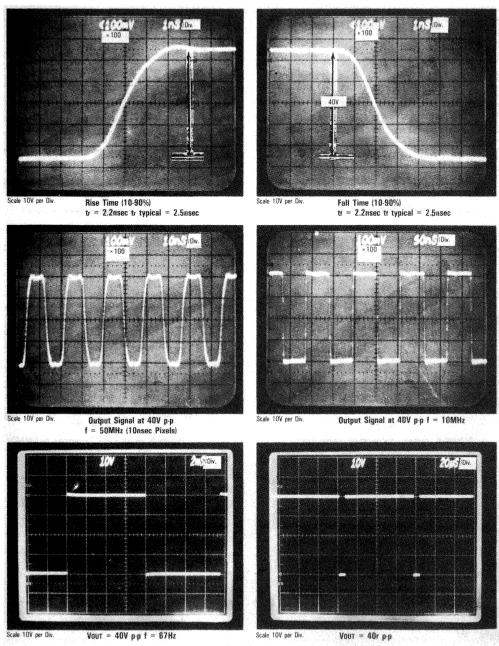

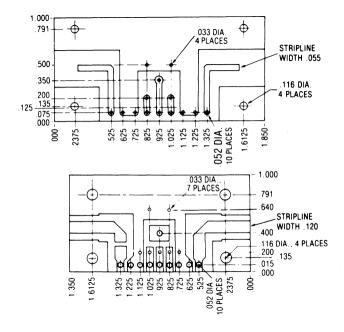

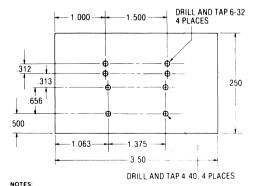

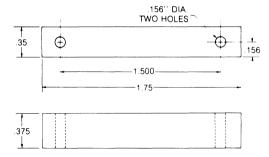

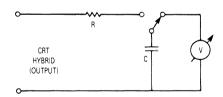

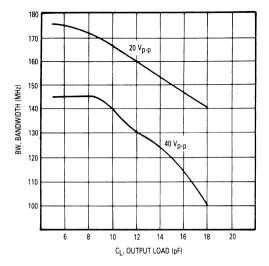

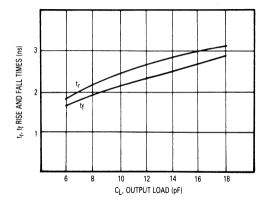

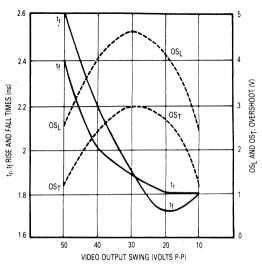

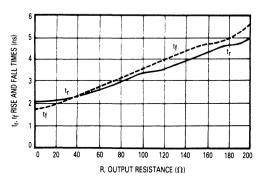

#### AN1021 A Hybrid Video Amplifier for High Resolution CRT Applications

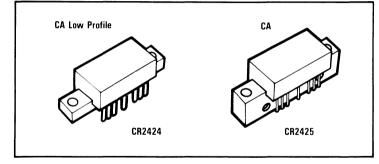

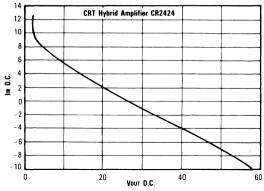

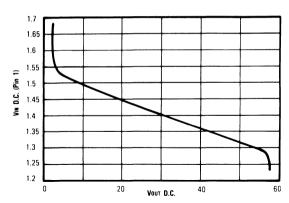

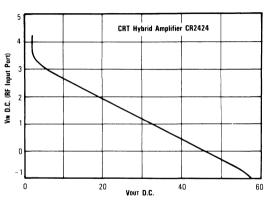

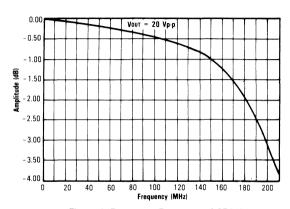

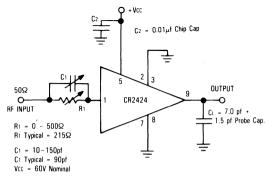

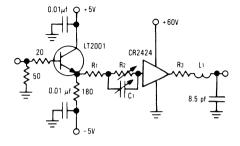

Many of the 1024 x 1024 and 1280 x 1024 pixel, 64kHz horizontal sweep rate CRTs used in CAD/CAM and high resolution graphics applications have not realized their potential performance because of the speed of their video amplifiers. The CR2424 and CR2425 video amplifiers are hybrid circuits designed for high resolution CRT applications. They feature less than 2.9ns rise and fall time for a 40V output swing, and provide a low power dissipation solution to the problem.

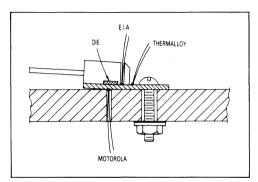

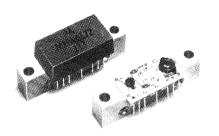

#### AN1022 Mechanical and Thermal Considerations in Using RF Linear Hybrid Amplifiers

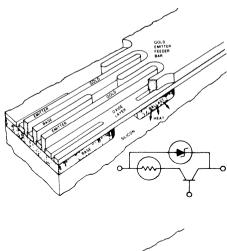

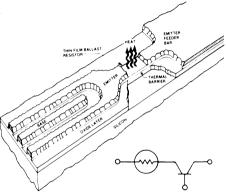

Motorola's thin film hybrid amplifiers are medium power (0.2W to 2.0W power output) broadband devices (1 to 1000MHz) that are biased in a class A mode for linear operation. To ensure a proper electrical and mechanical interface with adequate RF and thermal characteristics, certain guidelines are presented here so that the design engineer can obtain maximum electrical performance and the longest operating life.

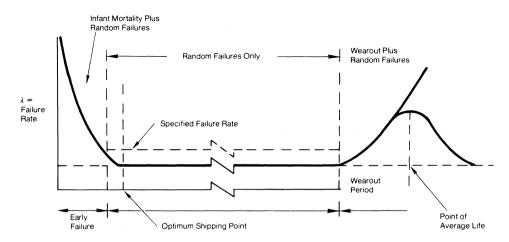

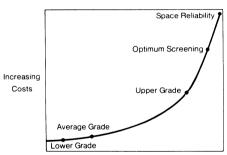

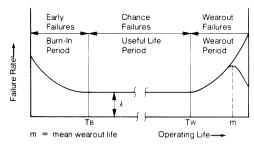

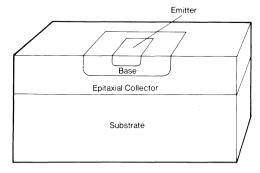

#### AN1025 Reliability Considerations in Design and Use of RF Integrated Circuits

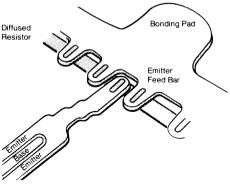

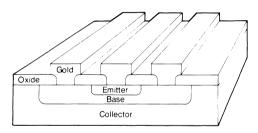

RF integrated circuits – located at strategic points in a CATV system – feature prominently in the overall reliability assessment. Low noise and distortion require state-of-the-art transistor structures. Gold metallization, thermal equilibrium and automated process control have resulted in transistor lifetimes of over 100 years. An overview of the physics of construction involved with the die and interconnects is discussed, together with definition of major reliability terms and an introduction to hardware and software microcircuit reliability tools.

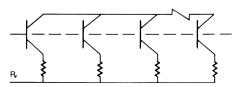

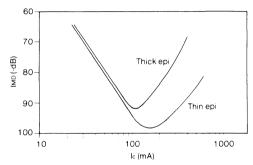

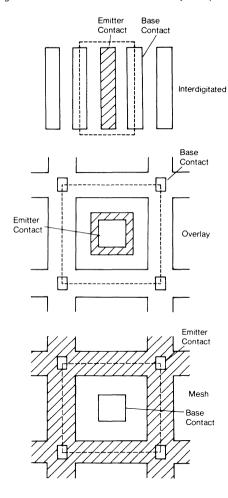

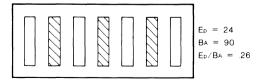

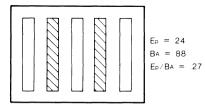

#### AN1027 Reliability/Performance Aspects of CATV Amplifier Design

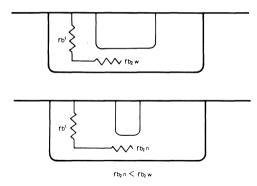

Discusses the reliability advantages offered by the RF hybrid amplifier used in CATV applications. The active part of the hybrid is the transistor — metallization, ballasting and ruggedness are reliability-related factors that must be considered by the device engineer when designing a high performance CATV transistor. Vertical and horizontal geometry and device distortion are performance-related factors that must also be taken into account. The relationship between these factors is examined, and life test data is presented to illustrate the advantages gained by careful device design.

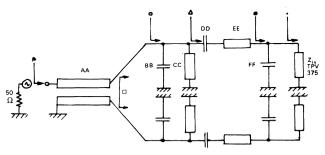

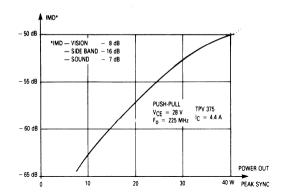

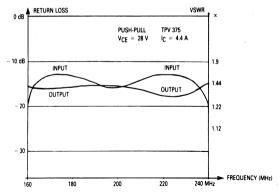

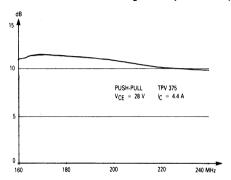

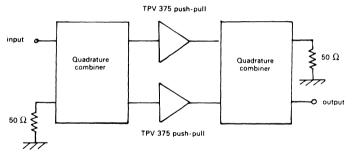

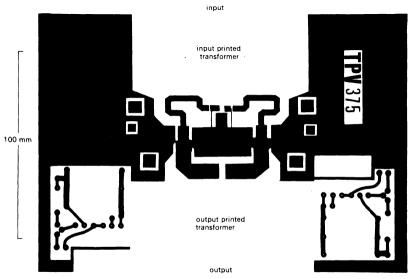

#### AN1028 35/50 Watt Broadband (160-240MHz) Push-Pull TV Amplifier Band III

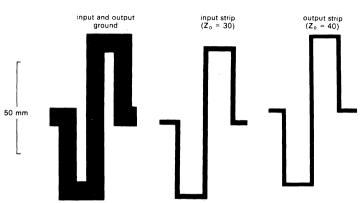

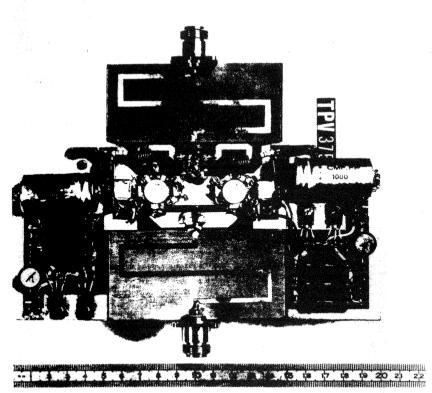

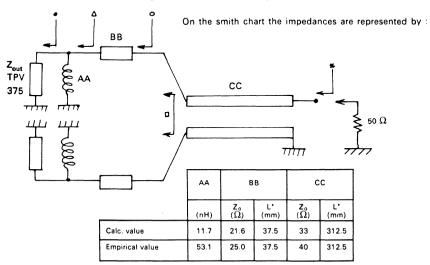

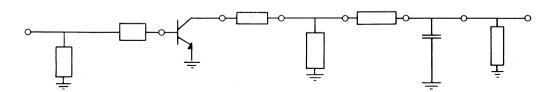

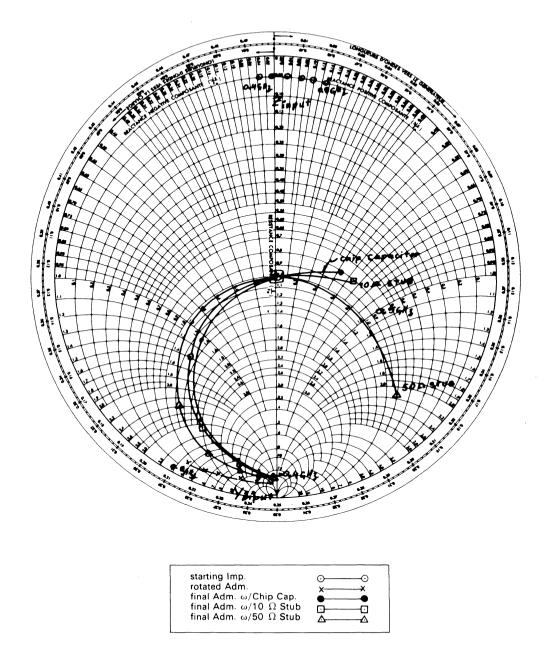

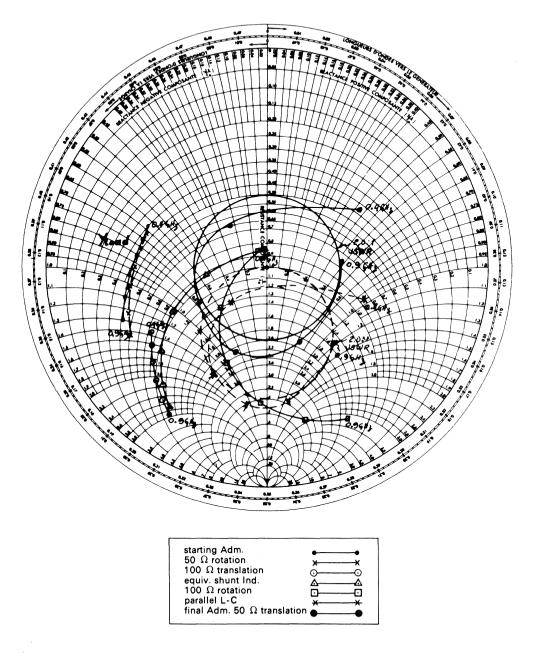

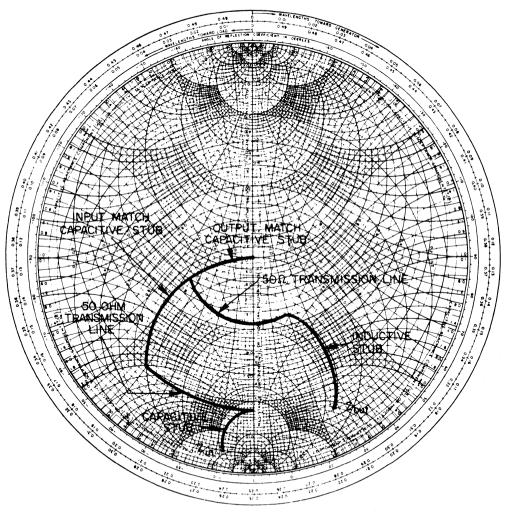

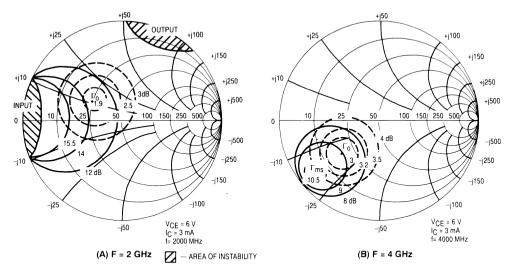

The main design aim for this broadband ultra-linear push-pull amplifier was to keep the design as simple as possible, in order to obtain the best performance from the two TPV375 transistors and to minimise the cost. A further target was to obtain the maximum gain by reducing input matching circuit losses. Includes circuit, background description. Smith charts and PCB layout.

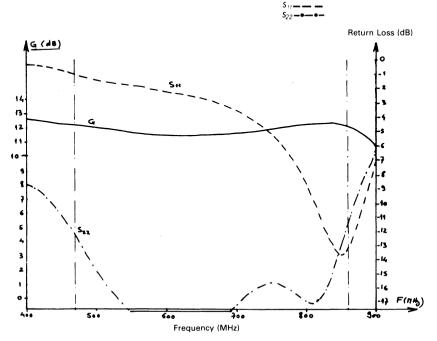

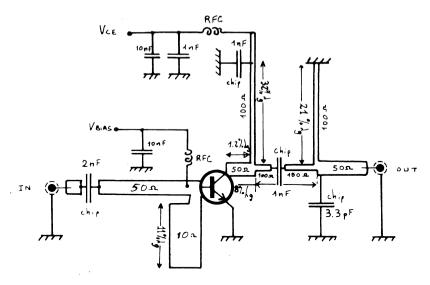

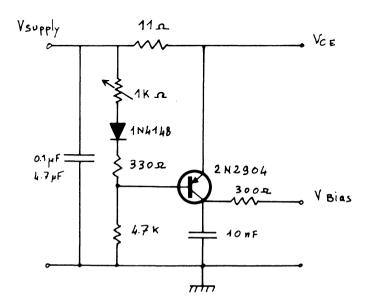

#### AN1029 TV Transposers Band IV and V Po = 0.5W/1.0W

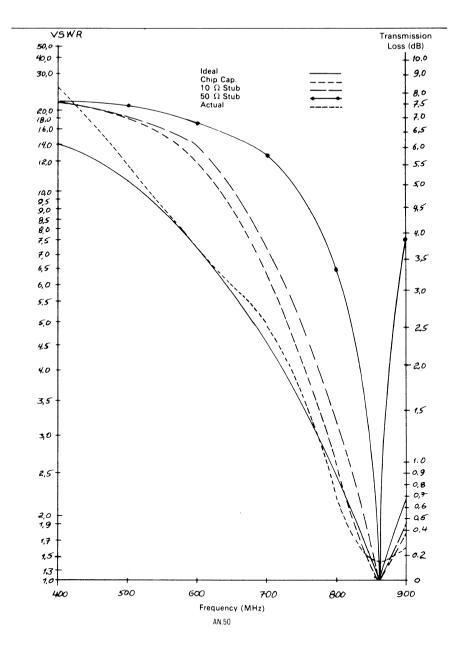

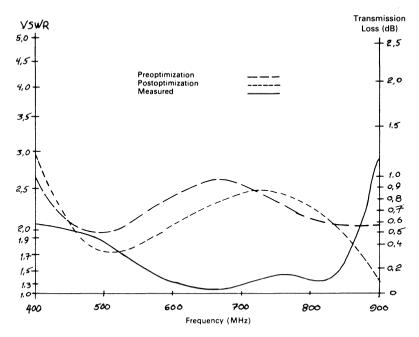

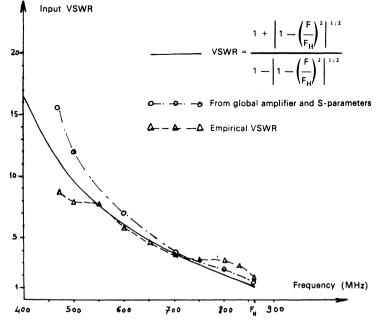

Describes the performance of a 470-860MHz broadband ultra linear amplifier designed for use in band IV and V TV transposers. The design is based on the TPV596, and is intended to be as inexpensive and straightforward as possible: the load line is defined to provide the correct match for peak power; VSWR at the collector is less than 2:1; input matching is designed to provide flat gain with decreasing frequency; and the design is optimized with a CAD program.

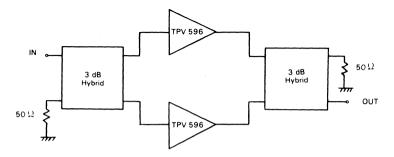

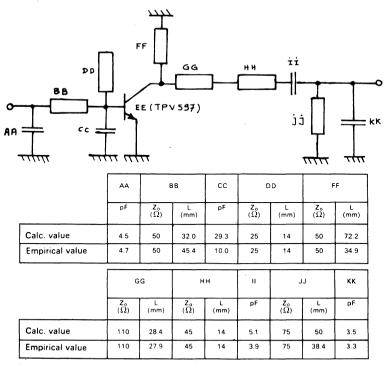

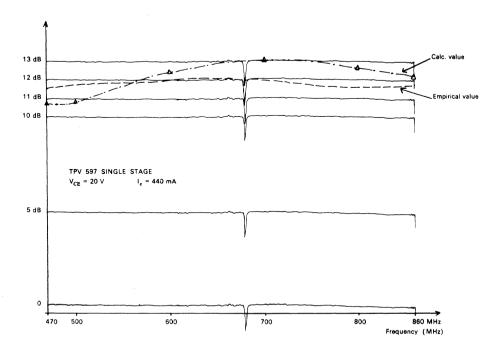

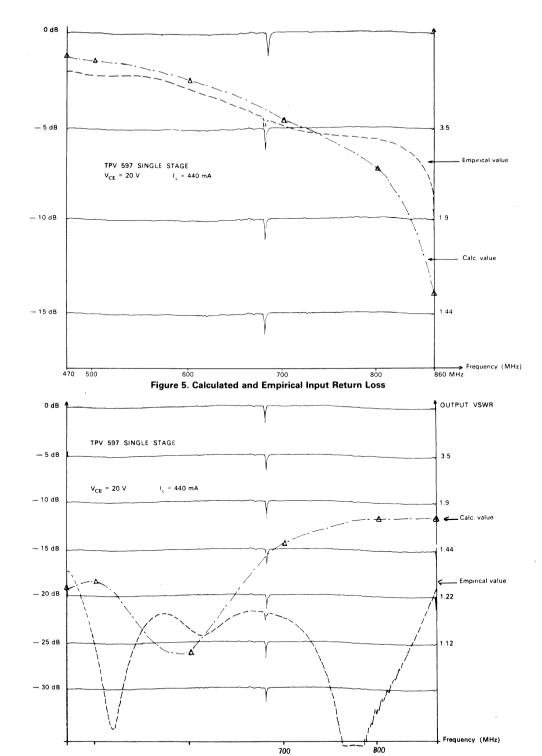

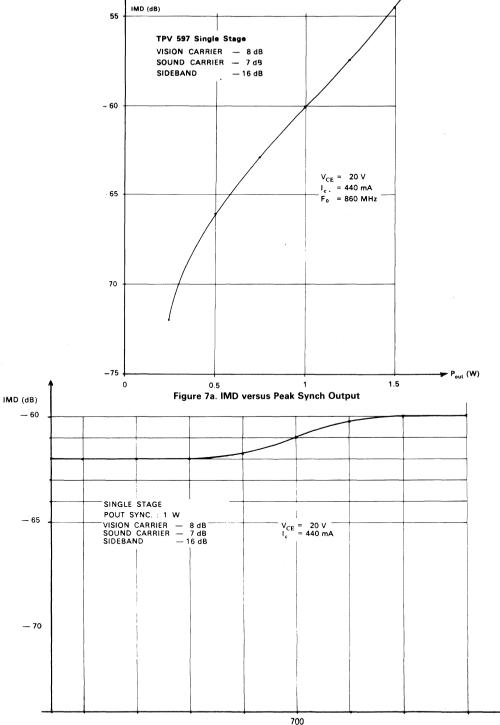

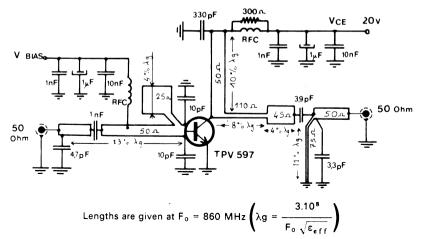

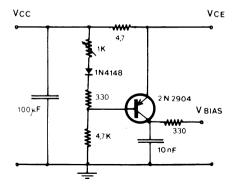

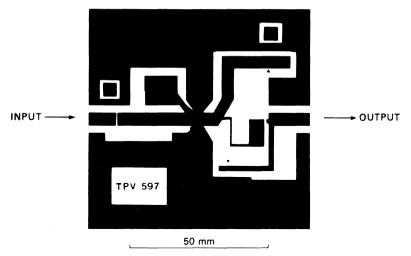

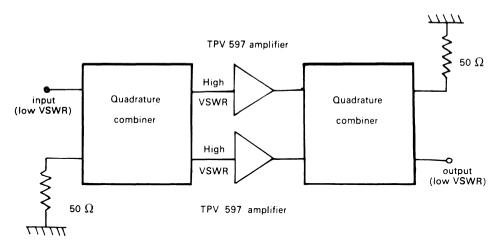

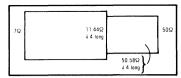

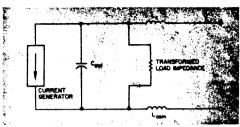

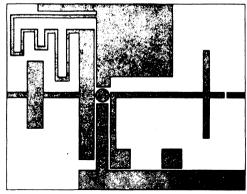

#### AN1030 1W/2W Broadband TV Amplifier Band IV and V

Describes the design and performance of a 470-860MHz broadband linear amplifier for use in band IV and V TV transposers, based on a TPV597 transistor. The design uses a reflection technique to achieve an insertioloss of 6dB per octave with 0dB for the highest frequency. Two amplifiers are connected together with

3dB quadrature hybrids to create a balanced amplifier avoiding the inconvenience of needing a good match of reflected power.

#### AN1032 How Load VSWR Affects Non-Linear Circuits

If your amplifiers pass lab tests but fail QC testing, the testing environment — not the product — is most likely at fault! Often the culprit is correlation of test systems — RF Correlation occurs only when target error limits are adhered to on a continuous basis among two or more testing stations. Such correlation is essential for nonlinear RF and microwave power amplifiers, whose circuits are extremely sensitive to the impedance of their loads. It is easy to compensate for the insertion loss errors in an attenuator, but much more difficult to compensate for load VSWR.

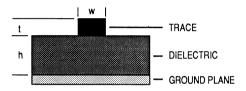

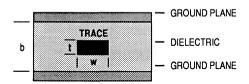

#### AN1033 Match Impedances in Microwave Amplifiers

The key to successful solid-state microwave power-amplifier design is impedance matching. In any high-frequency power-amplifier design, improper impedance matching will degrade stability and reduce circulefficiency. At microwave frequencies, this consideration is even more critical, since the transistor's bond-wire inductance and base-to-collector capacitance become significant elements in input/output impedance network design. Includes table of characteristic impedance and velocity factor for various width/height ratios and various materials.

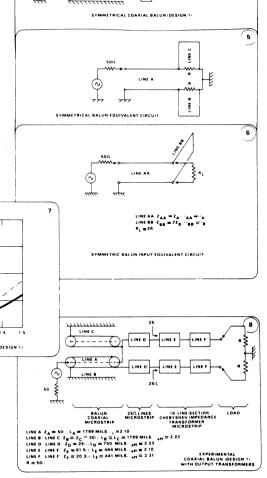

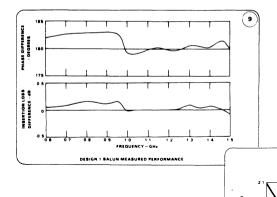

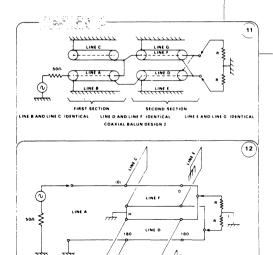

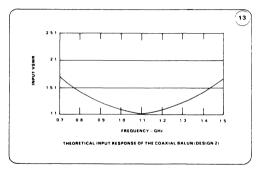

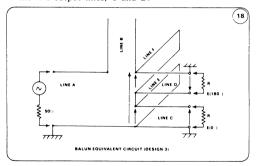

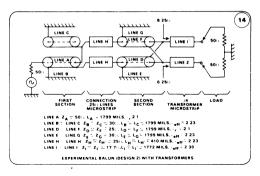

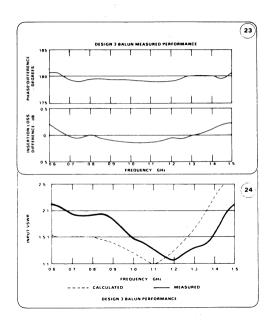

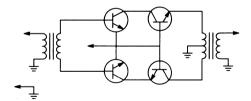

#### AN1034 Three Balun Designs for Push-Pull Amplifiers

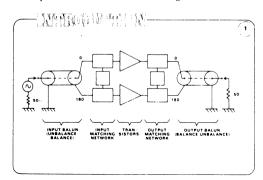

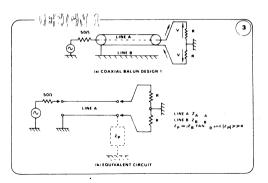

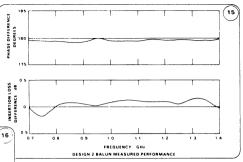

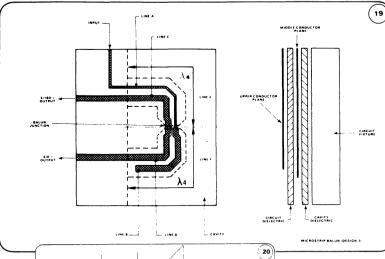

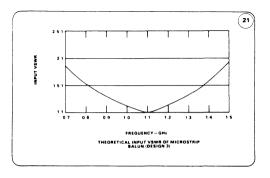

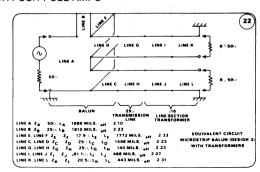

Single RF power transistors seldom satisfy today's design criteria; several devices must be coupled to obtain the required amplifier output power. The pushpull technique is often chosen because it allows input and output impedances to be connected in series for RF operation. Balun-transformers provide the key to push-pull design. This note develops three balun-transformers, culminating with a microstrip version. None of the baluns was tuned nor were the parasitic elements compensated. In this way, their deviation from their theoretical performance could be evaluated more easily.

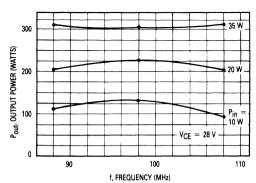

#### AN1037 Solid State Power Amplifier, 300W FM. 88-108MHz

A solid state power amplifier in a high efficiency FM transmitter can be made by operating a number of building block amplifiers in parallel. This note describes such a building block amplifier with high output power, high gain, good collector efficiency and broadband (88-108 MHz) frequency response. The design is simple, reproducible and reliable, and is suitable for several architectures. The amplifier has been developed using

a pair of TP9383 transistors in push-pull configuration; TP9383 is a double-diffused silicon epitaxial transistor using gold metallization and diffused ballast resistors for long operating life and ruggedness.

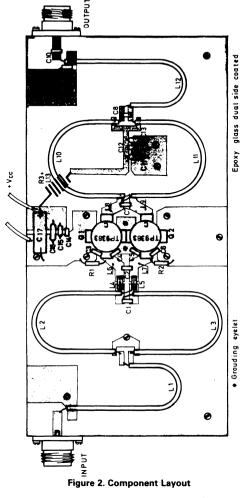

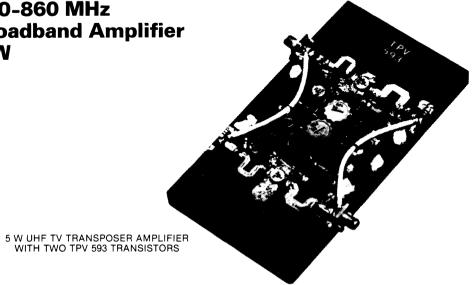

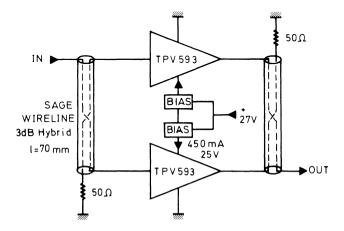

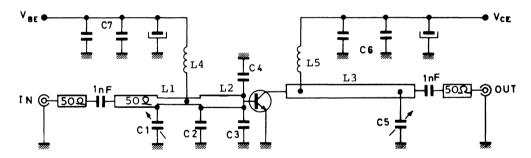

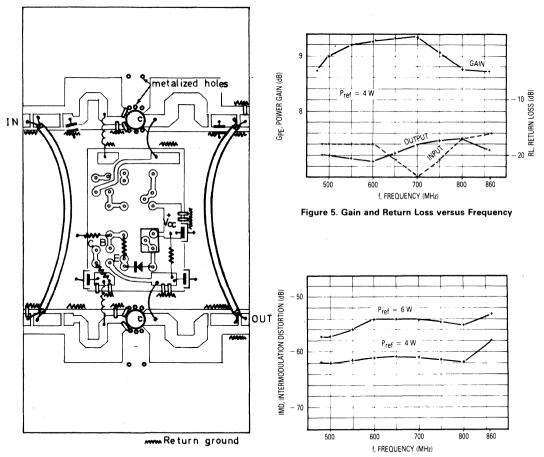

#### AN1039 470-860 MHz Broadband Amplifier 5W

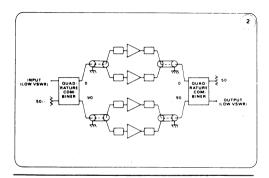

This note describes an ultra linear broadband (470-860MHz) amplifier developed for TV transposer applications. The amplifier incorporates two TPV593 transistors. Each transistor is used to build a separate broadband amplifier which are combined with 3dB hybrids. Includes circuit, parts list and PCB layout.

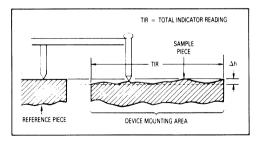

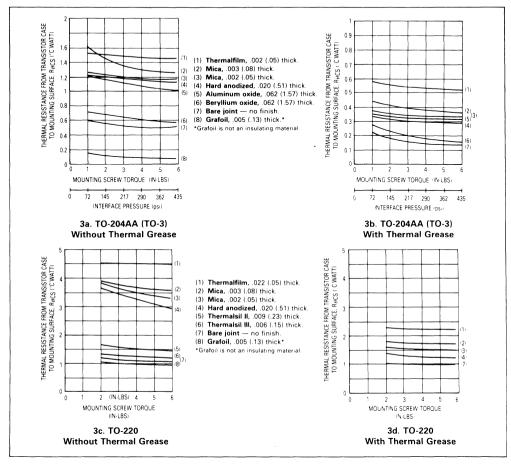

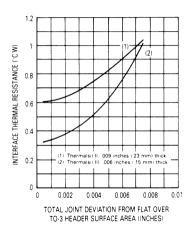

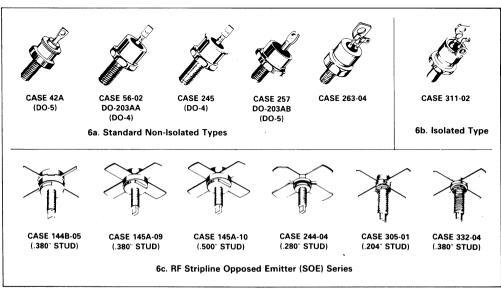

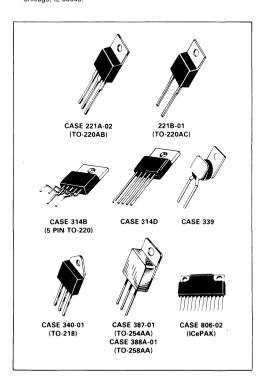

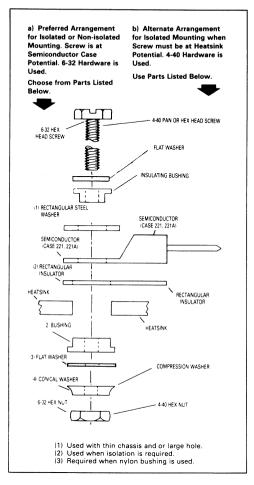

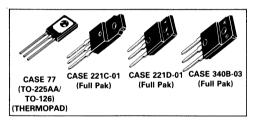

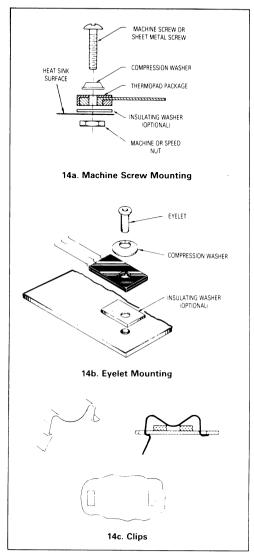

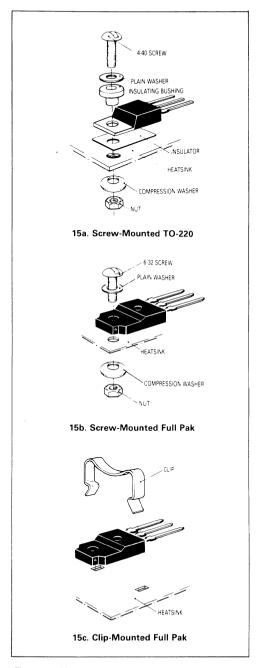

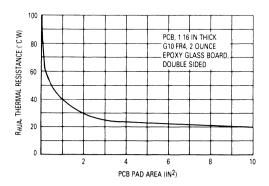

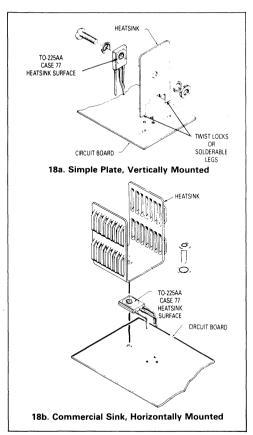

#### AN1040 Mounting Considerations for Power Semiconductors

The operating environment is a vital factor in setting current and power ratings of a semiconductor device. Reliability is increased considerably for relatively small reductions in junction temperature. Faulty mounting not only increases the thermal gradient between the device and its heat sink, but can also cause mechanical damage. This comprehensive note shows correct and incorrect methods of mounting all types of discrete packages, and discusses methods of thermal system evaluation.

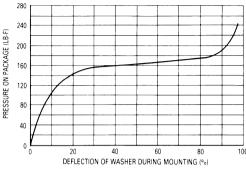

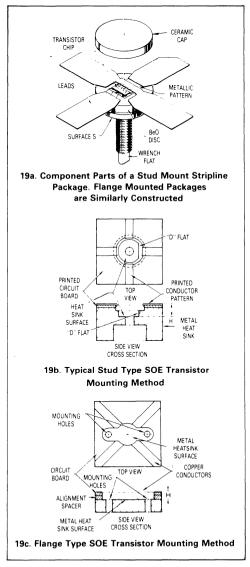

#### AN1041 Mounting Procedures for Very High Power RF Transistors

High power (200-600W) RF semiconductors such as the MRF153... and MRF141G... series dissipate an abnormally large amount of heat within a small physical area. Heat sink material, surface finish, mounting screws, washers and screw torque are extremely important factors in ensuring reliability. This note explains why.

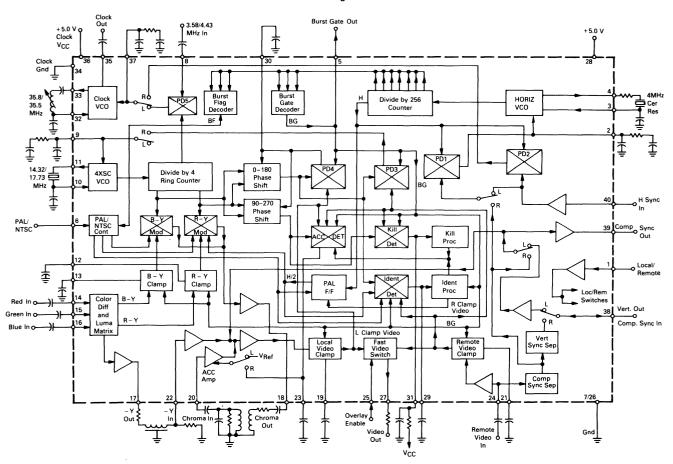

#### AN1044 The MC1378 — A Monolithic Composite Video Synchronizer

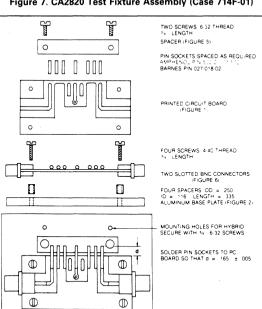

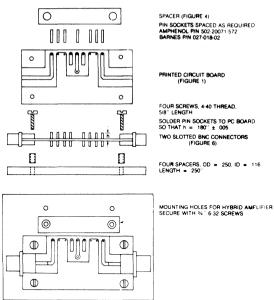

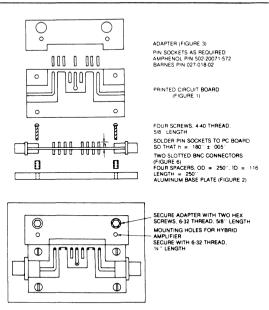

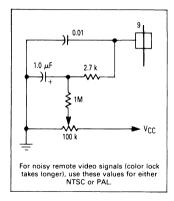

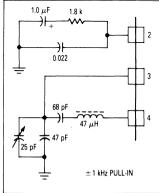

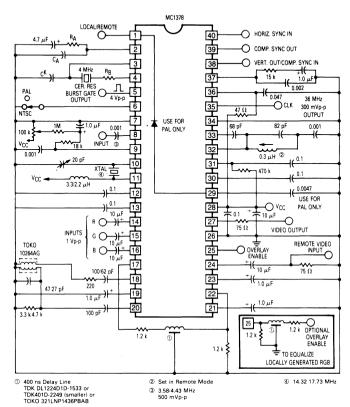

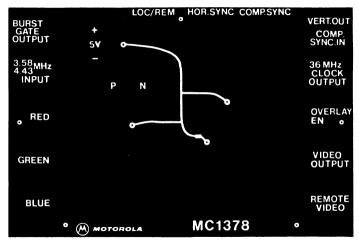

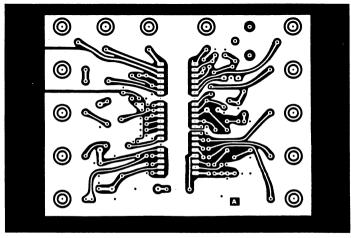

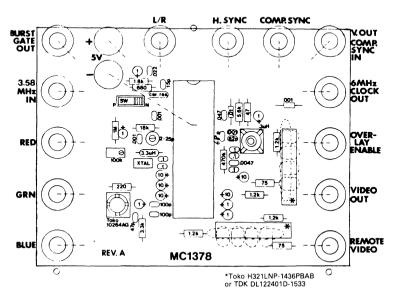

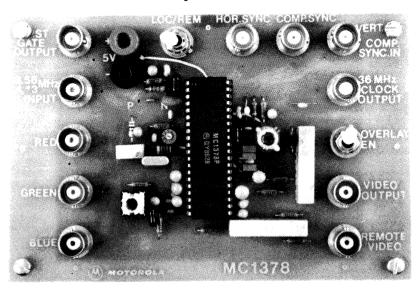

The MC1378 provides an interface between a remote composite colour video source and local RGB. On-chip circuitry can lock a local computer to the remote source, switching between local and remote signals to generate composite video overlays. This detailed note describes local and remote operation, picture-in-picture applications and the design of test fixtures to help system development. Printed circuit artwork for an evaluation board is provided. The NTSC/PAL colour encoder is similar to the MC1377, discussed in detail in AN932.

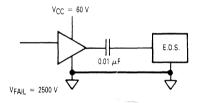

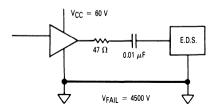

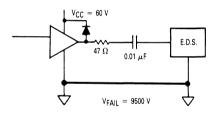

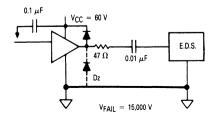

#### AN1047 Electrical Characteristics of the CR2424 and CR2425 CRT Driver Hybrid Amplifiers

Describes the circuit and thermal characteristics of the CR2424 and CR2425 CRT driver hybrid amplifiers, and discusses three different methods of protecting against damage by a tube arc. Provides details of bandwidth and rise and fall times.

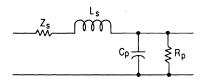

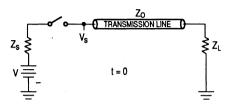

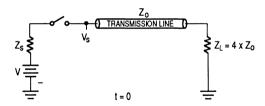

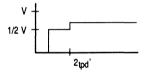

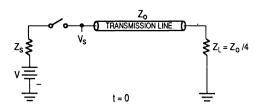

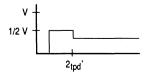

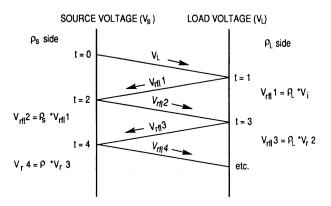

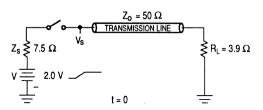

#### AN1061 Reflecting on Transmission Line Effects

In recent years, microprocessors and digital logic have seen substantial increases in line drive capability. The fast rise and fall times of modern devices make an understanding of transmission lines and their effects on system reliability a necessity. Includes a procedure for assessing possible transmission line problems in practical designs.

#### AN1080 External-Sync Power Supply with Universal Input Voltage Range for Monitors

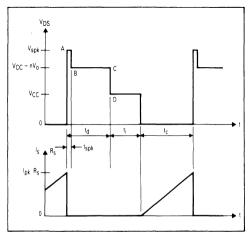

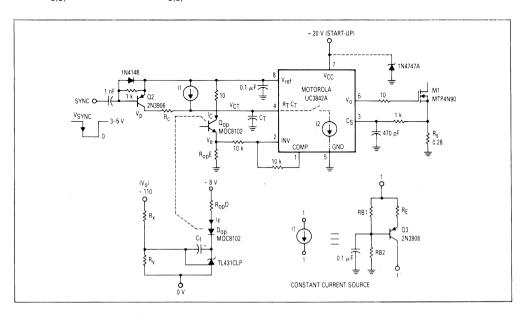

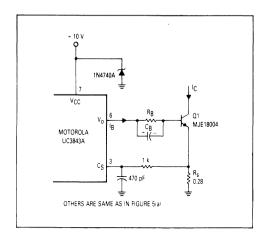

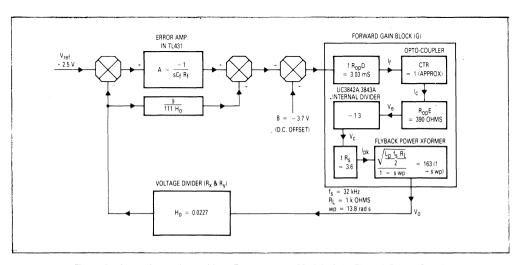

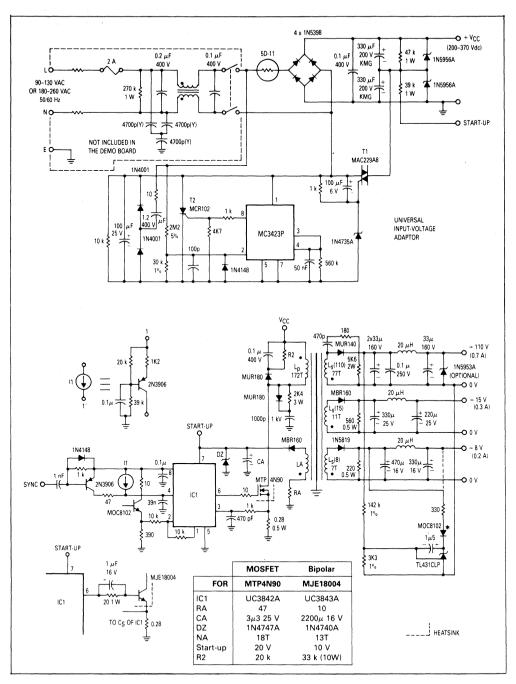

As the resolution of colour monitors increases, the performance and features of their power supplies becomes more critical. EMI/RFI generated by switching power supplies can adversely affect resolution if switching frequency is not synchronised to horizontal scanning frequency. This 90W flyback switching supply demonstrates the use of new high-performance devices in a low-cost design, and includes a new universal input voltage adapter.

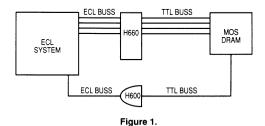

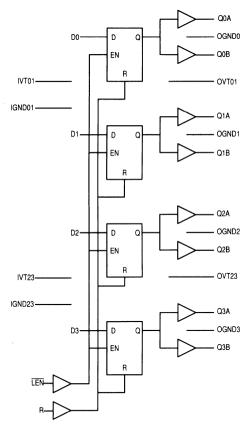

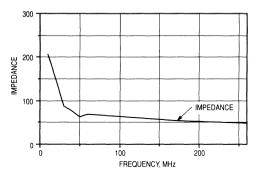

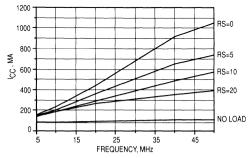

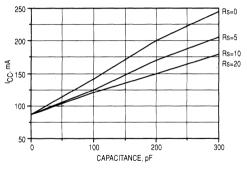

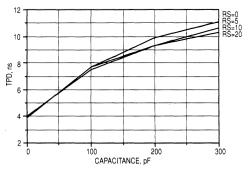

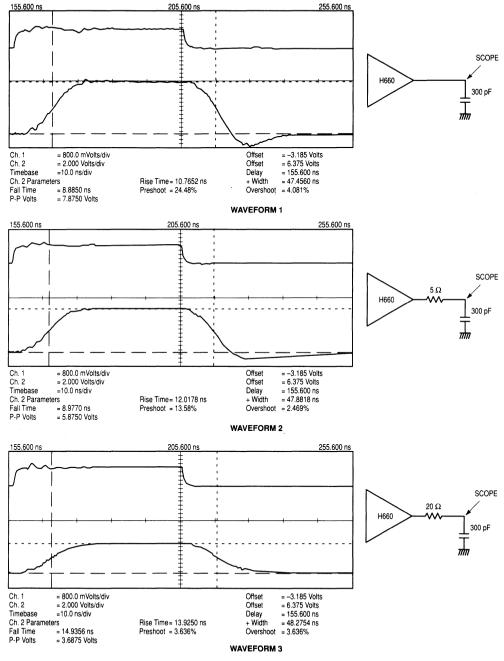

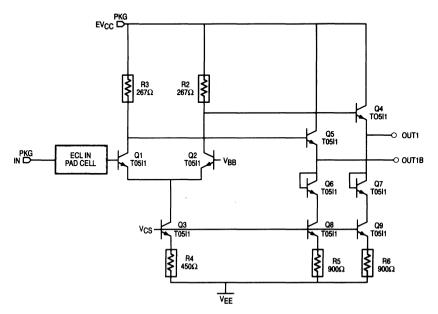

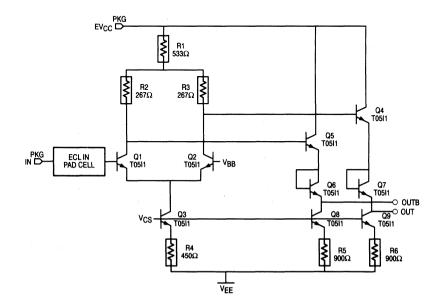

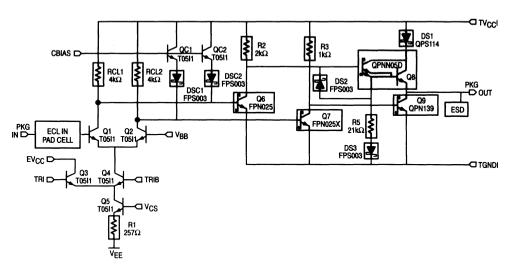

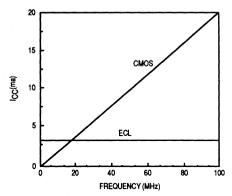

#### AN1092 Driving High Capacitance DRAMs in an ECL System

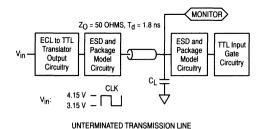

In systems where speed and efficiency are of utmost importance, designers often mix technologies to achieve the right combination of speed, power, cost and processing capability. Motorola's Emitter Coupled Logic (ECL) makes it possible to operate up to 1GHz clock rates. However, ECL speeds are not necessary in memory that is not accessed every clock cycle – a large CMOS DRAM is cheaper and uses less power and board space than ECL memory. The MC10H/100H660 4-bit ECL-TTL Load Reducing DRAM Driver was designed as a translator for such applications.

#### AN1106 Considerations in Using the MHW801 and MHW851 Series RF Power Modules

The MHW801 and MHW851 series of power modules are designed for use in cellular portable radios. A considerable amount of applications information is included in the data sheet; this note provides additional information concerning general electrical considerations, noise characteristics, gain control, circuit considerations and mounting.

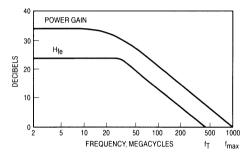

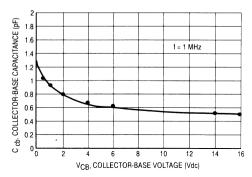

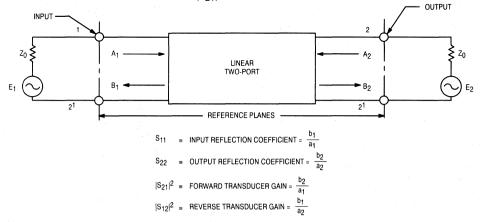

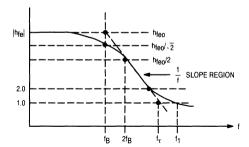

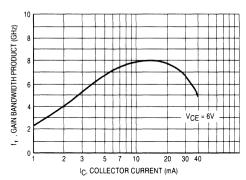

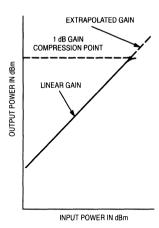

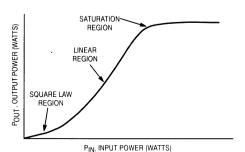

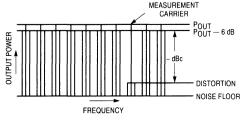

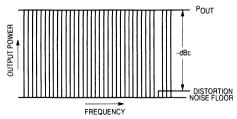

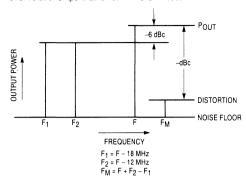

#### AN1107 Understanding RF Data Sheet Parameters

The data sheet is often the only source of information about the characteristics and capability of a product. This is especially true of RF devices, which have many unique specifications. It is therefore important that the manufacturer and designer speak a common language. This paper reviews the significance of the quoted values and highlights critical characteristics. Descriptions cover the procedures used to obtain impedance and thermal data, the importance of test circuits, low noise considerations and linearity requirements.

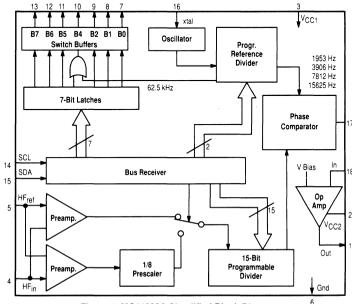

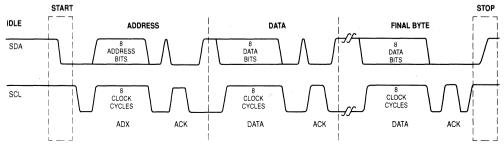

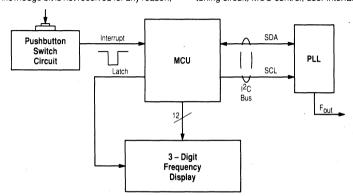

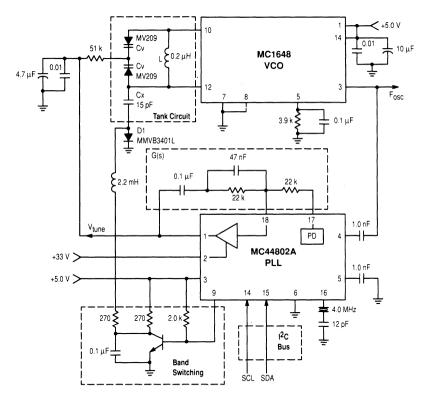

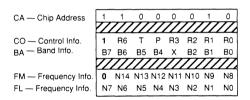

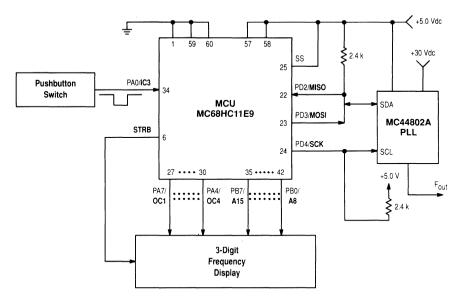

#### AN1122 Running the MC44802A PLL Circuit

The MC44802A provides the Phase Locked Loop (PLL) portion of a tuning circuit intended for TV, FM radio and set-top converter applications up to 1.3GHz; a complete tuning circuit is formed by adding a Voltage Controlled Oscillator (VCO) and mixer. The data sheet recommends use of an MCU for sending the control bytes that set the tuning frequency. This note describes a serial (IIC) interface with an MC68HC11E9 in a tuner design – the information is sufficiently general to allow almost any MCU to be used. Includes M68HC11 program listing.

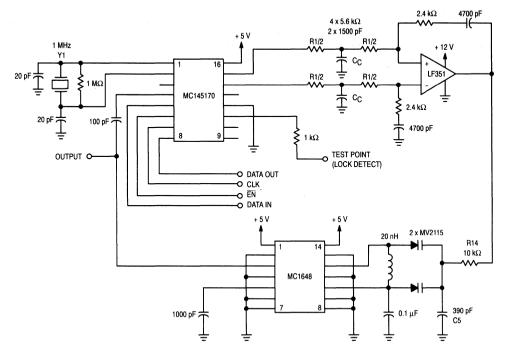

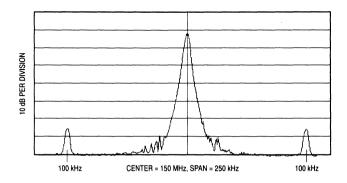

#### AN1207 The MC145170 in Basic HF and VHF Oscillators

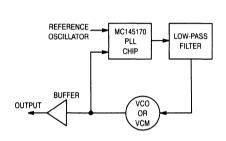

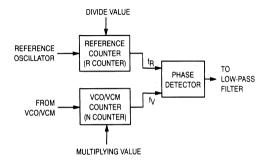

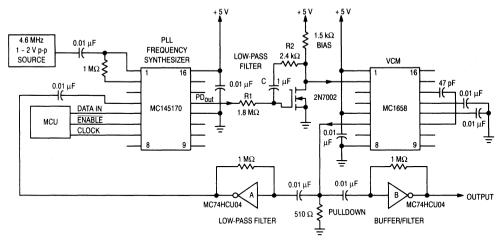

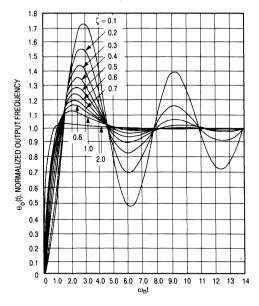

Frequency synthesisers such as the MC145170 use digital dividers which are typically under MCU control. Tuning in less than a millisecond can be achieved, and the device can generate many frequencies from a single reference source; the overall frequency capability ranges from a few Hertz to 160MHz. Typical applications include the carrier oscillator in transmitters, local oscillator in receivers, cellular phones, and multiple synchronised clocks in computers and other systems.

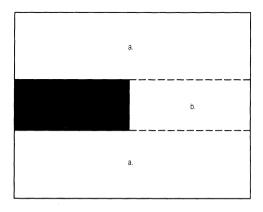

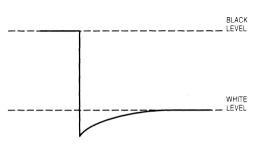

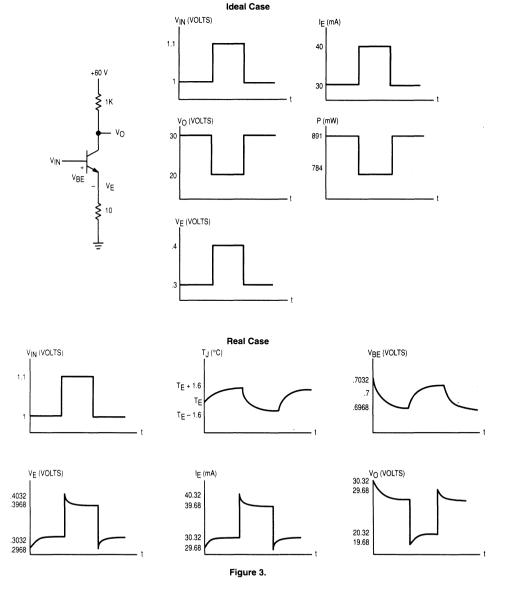

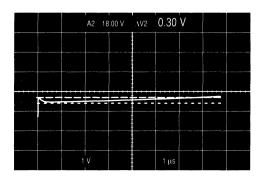

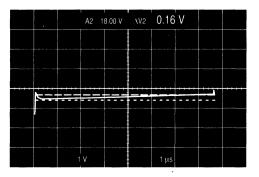

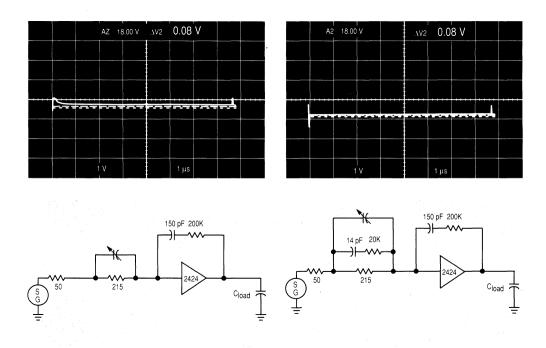

#### AN1306 Thermal Distortion in Video Amplifiers

Thermal distortion is a problem in many high resolution video amplifiers. It occurs when there are instantaneous power changes in the transistor stages, and if the problem remains uncompensated it leads to the visual effect known as smearing. This note discusses what smearing is, what causes thermal distortion, how to measure it, and how to compensate for it.

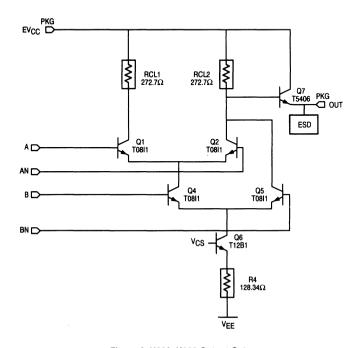

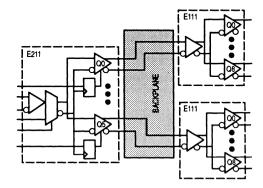

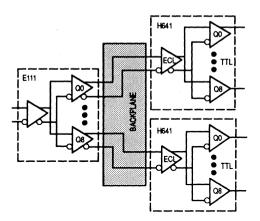

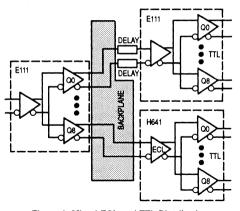

## AN1401 Using SPICE to Analyze the Effects of Board Layout on System Skew when Designing with the MC10/100H640 Family of Clock Drivers

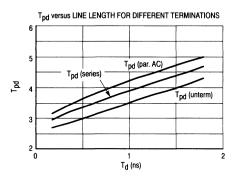

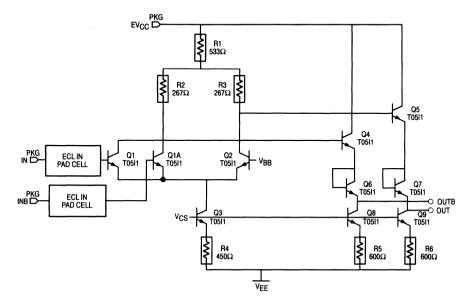

Illustrates the complex influences of board layout on the total skew of a system when designing with the MC10H/100H64x family of clock drivers. Discusses transmission line theory and the various termination techniques, and presents guidelines to assist designers in analyzing board layouts and loading schemes using SPICE simulations to predict and minimise the total skew of a system.

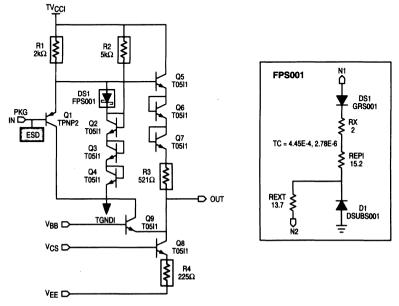

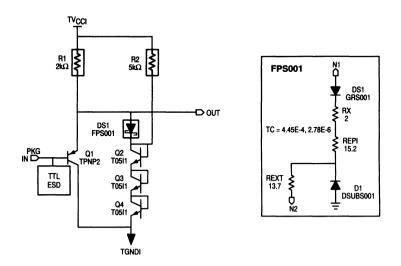

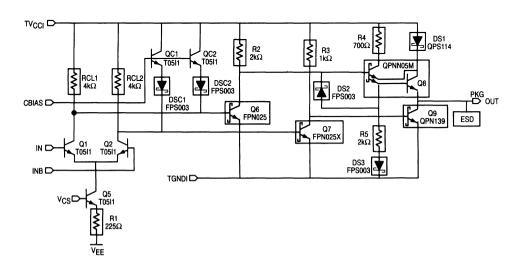

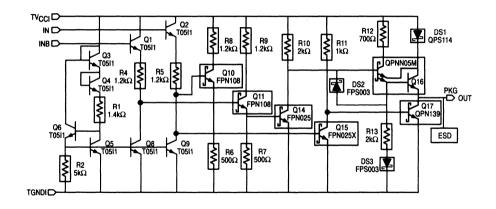

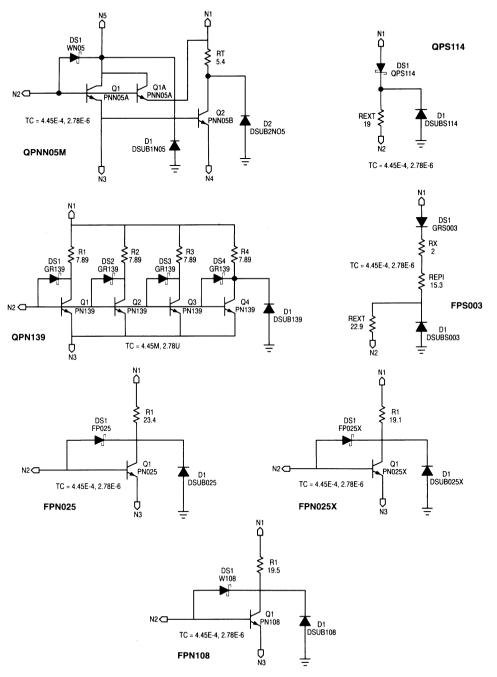

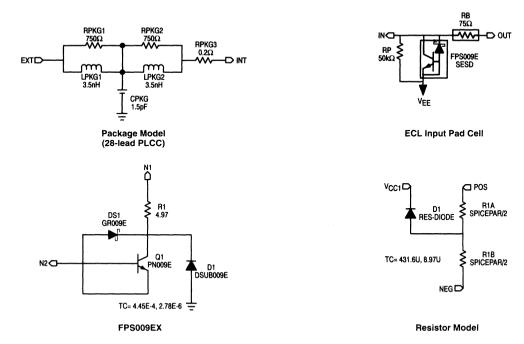

#### AN1402 MC10/100H00 Translator Family I/O SPICE Modelling Kit

The difficulties of designing high-speed, controlled-impedance PC boards – and the expense of reworking them – makes it essential for designers to model circuit performance prior to committing to a layout. This note provides sufficient information for basic SPICE analysis on the interconnect traces driving or being driven by the 'H600, 'H601, 'H602, 'H603, 'H604, 'H605, 'H606 and 'H607 translator chips. It includes schematics of the input, output and ESD structures, and package

models which may affect the waveforms. A SPICE parameter set for the referenced devices is provided.

#### AN1404 ECLinPS Circuit Performance at Non-Standard VIH Levels

When ECLinPS devices are interfaced to other technologies there may be times when the input voltages do not meet the specification detailed in the ECLinPS data book. This application note discusses the consequences of driving ECLinPS devices with an Input Voltage HIGH level which is outside the specification.

#### AN1405 ECL Clock Distribution Techniques

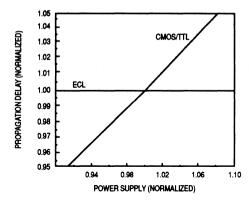

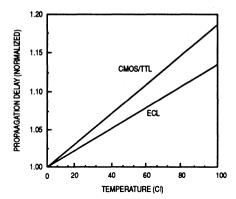

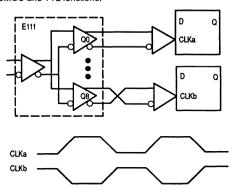

Clock skew – the time difference between supposedly simultaneous clock transitions within a system – is one of the main factors limiting system performance at high frequencies. If clock skew can be reduced, designers can increase performance without using faster logic or more complex and more expensive architectures. Emitter Coupled Logic (ECL) technologies offer a number of advantages over the CMOS and TTL alternatives; this note describes the advantages, the three skew problem areas, and methods of clock distribution to minimise skew.

#### EB27A Get 300 Watts PEP Linear Across 2 to 30MHz from this Push-Pull Amplifier

Includes circuit, PCB artwork and layout for a 300W push-pull linear amplifier based on two MRF422s, designed to operate over the 2 to 30MHz band. An MC1723 voltage regulator is used as a bias supply.

#### EB29 The Common Emitter TO-39 and its Advantages

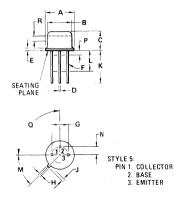

The Common Emitter TO-39 package differs from conventional TO-39s or TO-5s in that the emitter – not the collector – is connected to the metal case. With NPN transistors this configuration allows direct connection of the can to RF and negative DC ground in many class B and C circuits. There are two important advantages: by connecting the case to RF ground, emitter inductance is reduced and gain increased by 3 to 5 dB over that of comparable, conventionally wired transistors. And the case may be directly pressed, clipped, or soldered to the heat sink with no effect on RF performance.

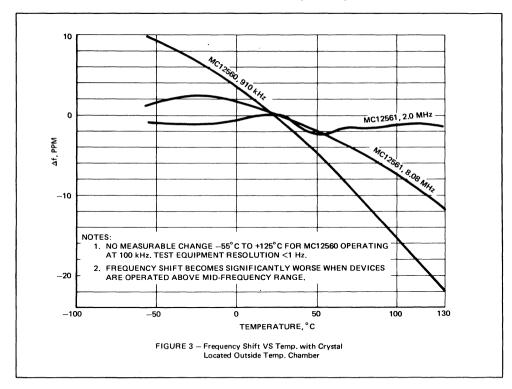

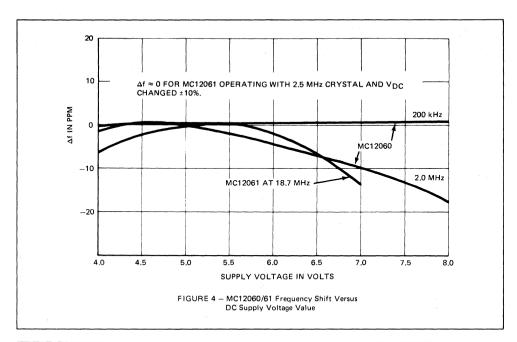

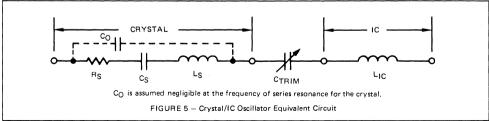

#### EB59 Predict Frequency Accuracy for MC12060 and MC12061 Crystal Oscillator Circuits

Crystal oscillators are used to generate a precise and highly stable signal. Such circuits typically provide this signal at a frequency close to the resonant frequency of their crystal. However, circuit components and other factors external to the crystal influence its natural resonance to some degree, an effect often referred to as "pulling" or "warping". This bulletin discusses the variation in crystal frequency as a function of different

ICs, temperature and DC supply voltage to help the designer to predict the amount of frequency pull in a particular design.

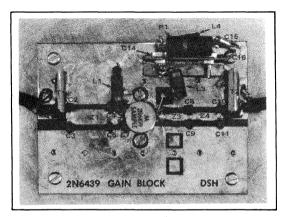

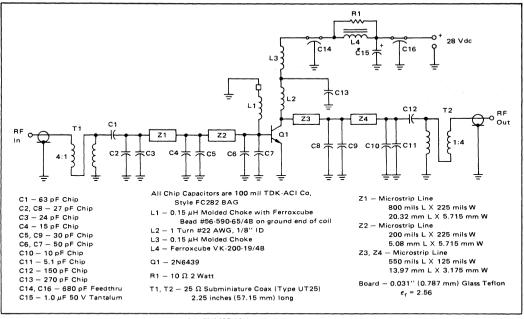

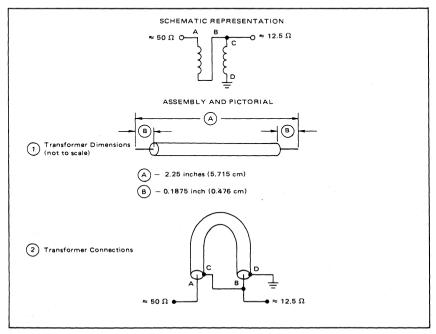

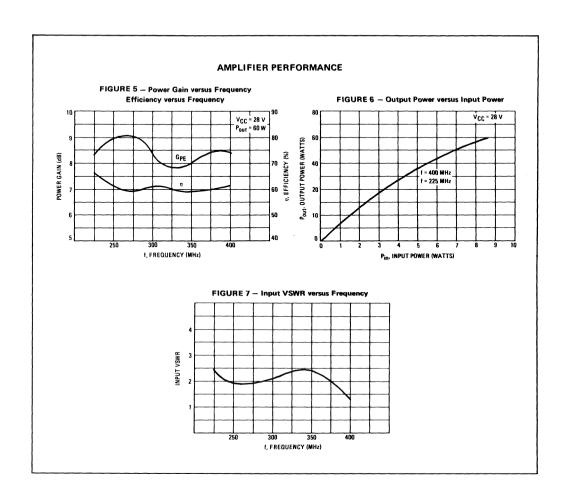

#### EB77 A 60 Watt 225-400MHz Amplifier – 2N6439

This bulletin describes a 60 watt, 28 volt broadband amplifier covering the 225-400 MHz military communications band. The amplifier may be used singly as a 60 watt output stage in a 225-400 MHz transmitter; by using two of these amplifiers combined with quadrature couplers a 100 watt output amplifier stage may be constructed. The circuit is designed to be driven from a 50 ohm source and work into a nominal 50 ohm load.

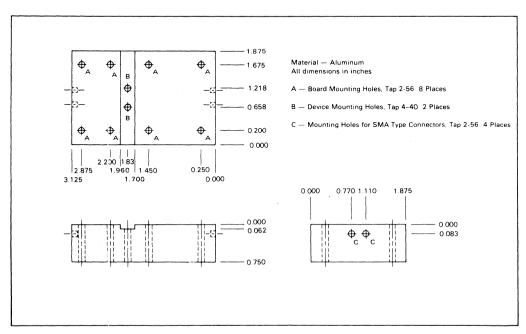

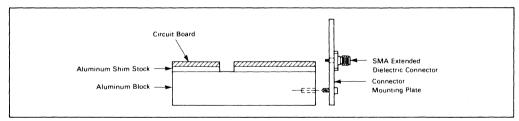

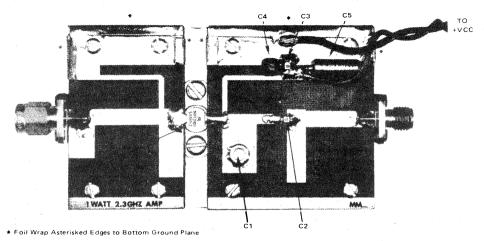

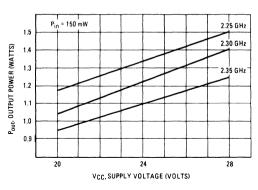

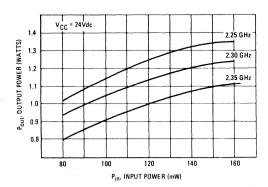

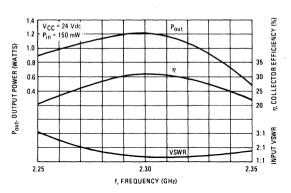

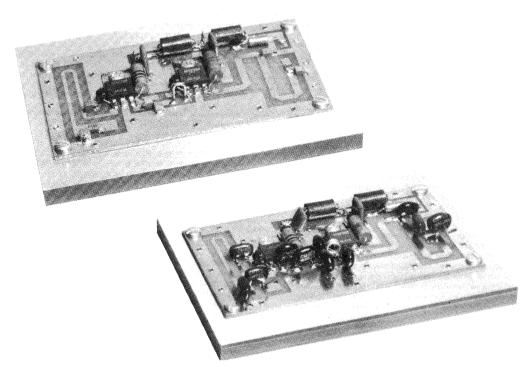

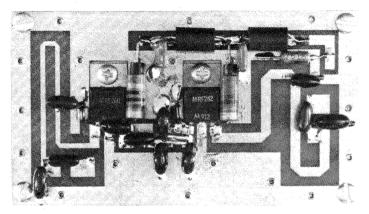

#### EB89 A 1 Watt. 2.3GHz Amplifier

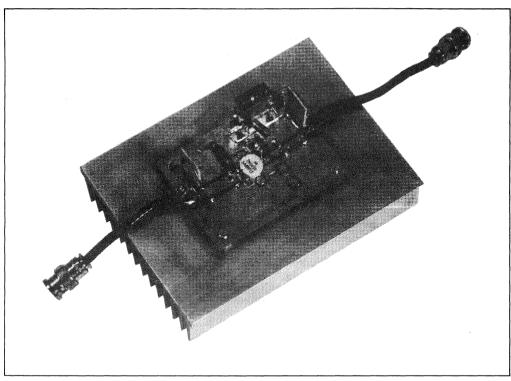

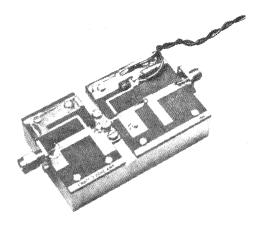

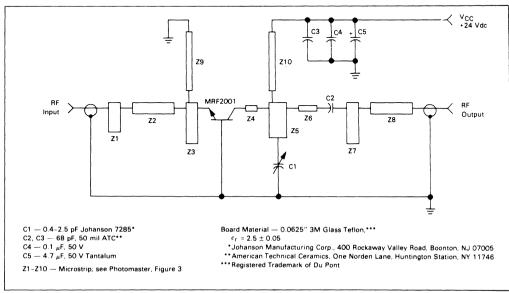

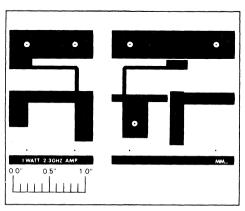

This S-band amplifier features simplicity and repeatability, delivering 8dB minimum gain at 1 watt output on a 24V supply. It uses an MRF2001 transistor in a common base, class C configuration, and is tunable from 2.25 to 2.35GHz. Applications include micowave communications and other systems requiring medium power, narrow band amplification. The Bulletin stresses the importance of physical construction as well as electrical design.

#### EB90 Low-Cost VHF Amplifier Has Broadband Performance

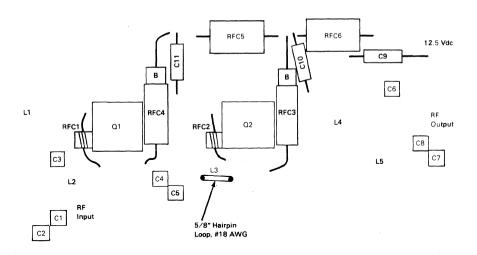

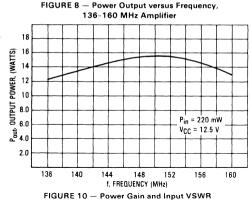

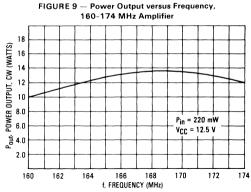

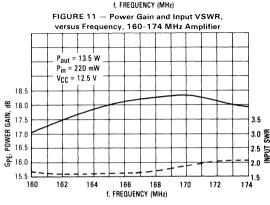

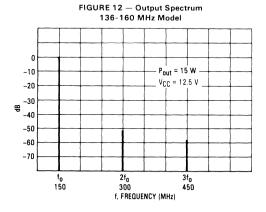

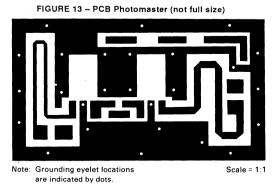

This bulletin presents two VHF amplifier designs intended for FM or CW service in the 136-174 MHz band. Both feature the Motorola MRF260 and MRF262 plastic encased VHF transistors which are rated at 5.0 W and 15 W power output respectively. The devices are packaged in a standard T0-220 silicone epoxy case with the emitter wired to the metal tab and centre lead of the device. This common emitter configuration results in good RF performance, improved thermal conductivity, and ease of mounting in an RF amplifier by connecting the transistor mounting flange to RF and DC ground.

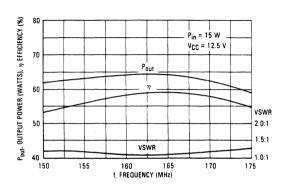

#### EB93 60 Watt VHF Amplifier Uses Splitting/Combining Techniques

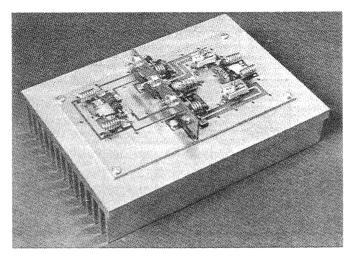

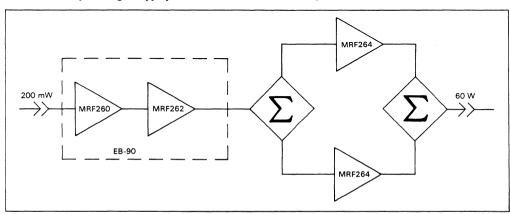

Proven combining techniques can be used to obtain higher output power and added reliability at VHF. Simple matching networks and power transistors with moderate gain can produce performance comparable to that of a single-stage amplifier with a larger, more expensive device. Though not the ultimate answer, the splitter/combiner method has distinct advantages over designs that force transistors into a parallel configuration. This 60 W amplifier operates from 150 to 175 MHz and features two low-cost MRF264 transistors. The design uses a modified Wilkinson combiner technique to produce 60W output with a drive level of 15W.

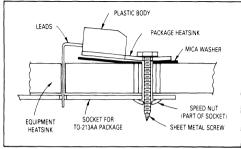

#### EB107 Mounting Considerations for Motorola RF Power Modules

The packaging used for Motorola RF Power Modules consists of a copper flange on which the ceramic substrates are soldered, and a non-conductive cover which is either a snap-on design or attached by epoxy. The substrates are either 96% Alumina, 95.5% Alumina, or 99% Beryllium Oxide, and are attached to the copper flange using lead-tin or indium based soft solders. This bulletin discusses the mechanical factors that should be considered when mounting these modules in equipment.

#### EB411 A Digital Video Prototyping System

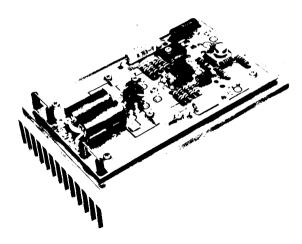

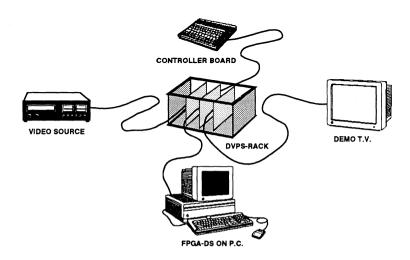

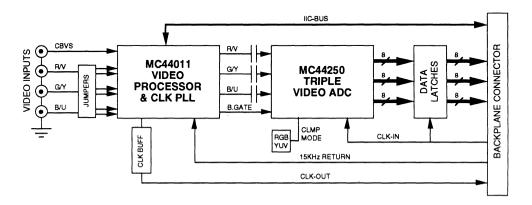

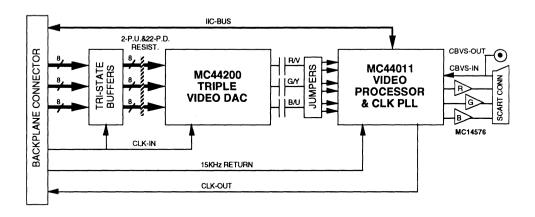

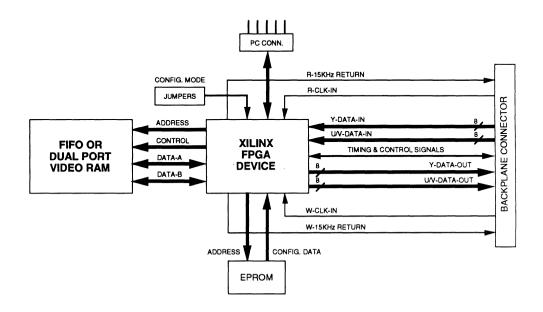

This bulletin describes a Digital Video Prototyping System (DVPS) developed using Motorola's latest multimedia devices, together with a PC-based Field Programmable Gate Array (FPGA) development system. It is designed to provide a fast and effective means of prototyping and demonstrating digital video processing functions. A Reference Section lists datasheets and user manuals containing detailed descriptions and information on the devices. The DVPS has been successfully used to implement two TV sub-systems, namely a Picture-In-Picture Processor and a 4:3 to 16:9 Picture Processor, which are also described.

# **Applications Documents**

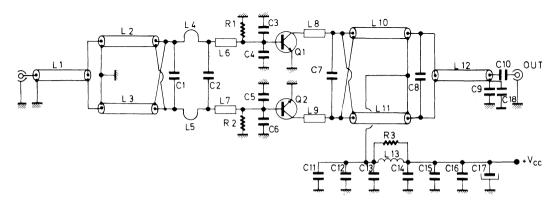

## 300W, 88–108MHz Amplifier using the TP1940 MOSFETs Push-pull Transistor

By Georges Chambaudu Motorola Semiconducteurs Bordeaux SA

#### INTRODUCTION

The TP1940 is a high power, high gain and broadband device with low Reverse Transfer Capacitance, C<sub>rss</sub>. It makes possible fully solid-state transmitters of above 5 kW for FM broadcasts

Like all MOS devices, it is susceptible to damage from electrostatic discharge. Observe reasonable precautions in handling and packaging it.

The 300 W amplifier described in this Application Note has these features:

- · Operates from a 50 V supply

- High power gain

- Compact physical layout

- · High efficiency

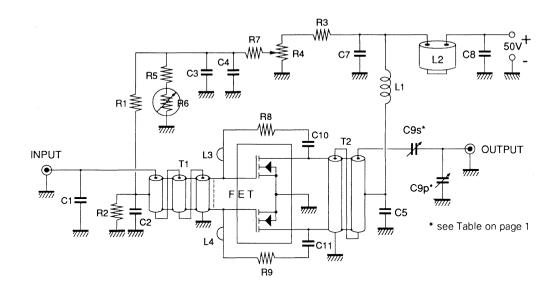

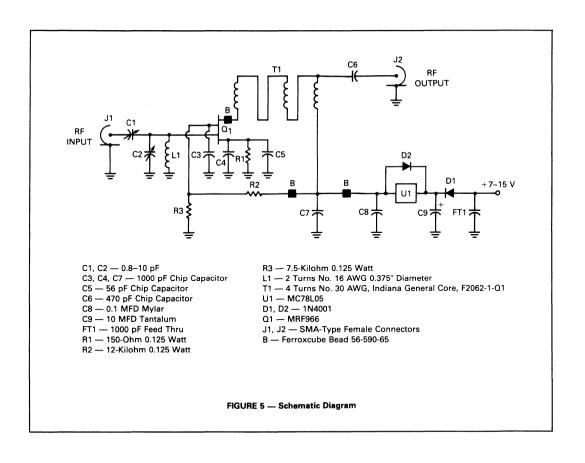

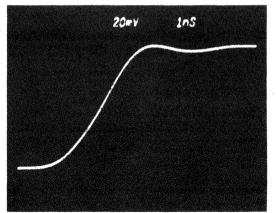

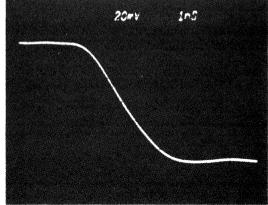

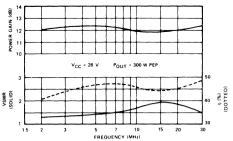

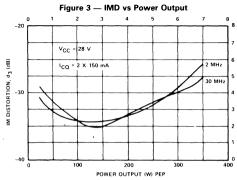

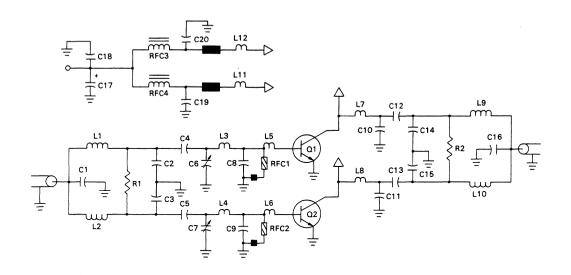

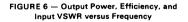

Typical data for the circuit in Figure 2 are given below.

FUNCTIONAL TESTS ( $V_{DD} = 50 \text{ V}$ ,  $P_{out} = 300 \text{ W}$ ,  $I_{dg} = 2 \times 200 \text{ mA}$ )

|         | Option 1 (with C9p and without C9s) |       | Option 2 (with C9s and without C9p) |       |

|---------|-------------------------------------|-------|-------------------------------------|-------|

| f (MHz) | G <sub>A</sub> (dB)                 | η (%) | G <sub>A</sub> (dB)                 | η (%) |

| 108     | 19.2                                | 62    | 18.3                                | 65.4  |

| 98      | 19.7                                | 62.6  | 19.1                                | 68    |

| 88      | 19.4                                | 64    | 19.6                                | 66.6  |

#### Note:

- 1. Bias increases counter-clockwise with R4.

- 2. Bias shown is set for 200 mA at 50 V.

- 3. A copper heat spreader must be mounted on, or laid on top of, a heat sink with thermal grease interface.

- 4. Drain efficiency can be increased by:

- a. Lowering Drain Idle current (power gain will be reduced by 1-2 dB).

- b. Increasing the value of feedback resistors R8 and R9. This will change the Gain–Frequency slope and Input VSWR. The value of C1 must be raised.

- 5. In addition to the normal cooling of the units, some air flow is recommended over the top side of the amplifier boards.

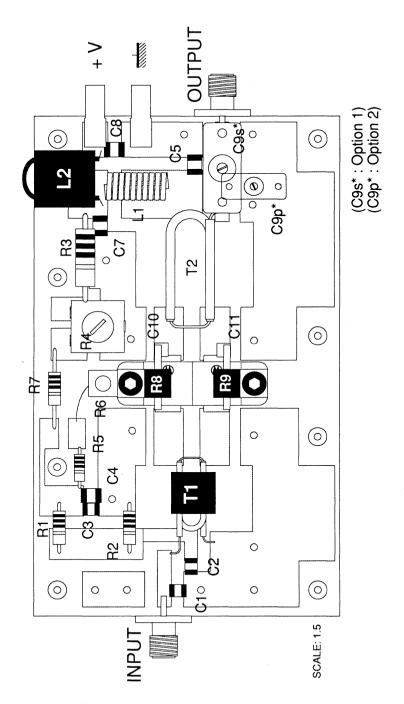

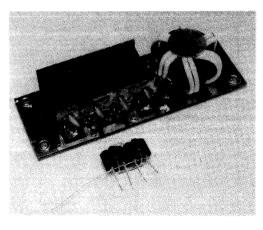

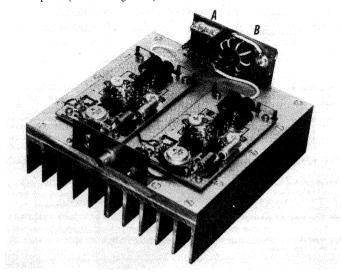

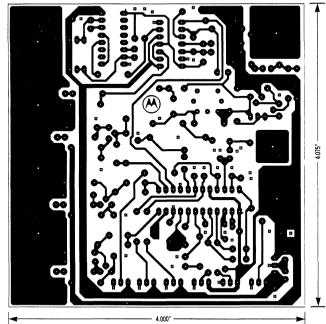

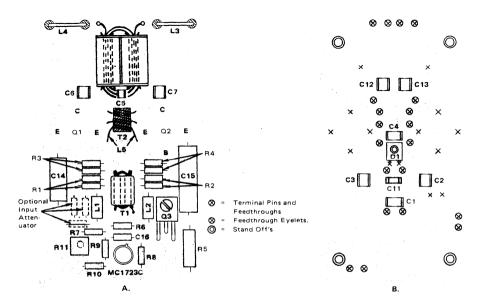

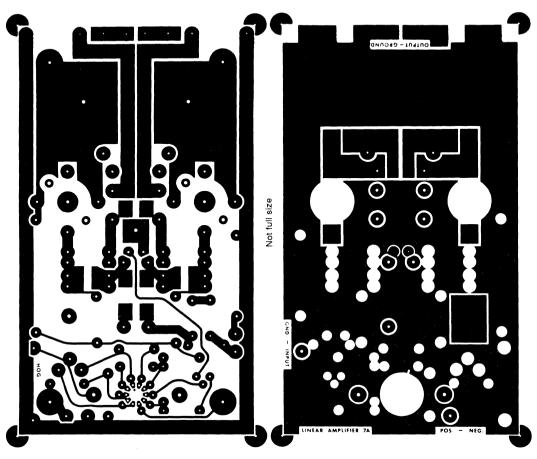

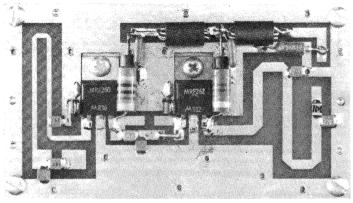

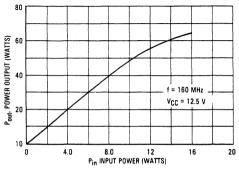

Figure 1. Component layout of 300 W amplifier

| C1       | 24pF Ceramic Chip                                                                 | R5     | $6.8$ - $8.2$ K $\Omega$ 1/4W (depending on FET $g_{fs}$ )                                                |

|----------|-----------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------|

| C2       | 1000pF Ceramic Chip                                                               | R6     | Thermistor, $10 \mathrm{K}\Omega$ at $25^{\circ}\mathrm{C}/2.5\mathrm{K}\Omega$ at $75^{\circ}\mathrm{C}$ |

| C3, C10, |                                                                                   | R7     | 2KΩ 1/2W                                                                                                  |

| C11      | 0.1μF Ceramic Chip                                                                | R8, R9 | KDI Pyrofilm PPR515-20-3 or EMC Technologie                                                               |

| C4, C5   | 1000pF Ceramic Chip                                                               |        | model 5310 or equivalent $100\Omega$                                                                      |

| C7       | 5000pF Ceramic Chip                                                               | L1     | 10 turns AWG #16 enamelled Wire, 0.2" I.D.                                                                |

| C8       | $0.47\mu\text{F}$ Ceramic Chip or lower values in parallel                        | L2     | Ferrite beads, 1.5 μH Total                                                                               |

|          | to reach the value indicated.                                                     | L3, L4 | Lead lengths of R8 and R9, 0.6" total.                                                                    |

| С9р      | ARCO 404, 8-60pF or equivalent                                                    | FET    | TP1940                                                                                                    |

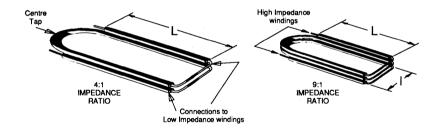

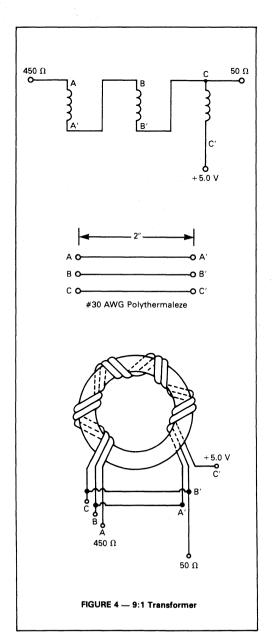

| C9s      | ARCO 425, 40-200pF or equivalent                                                  | T1     | 9:1 impedance ratio (input transformer)                                                                   |

| Note 1:  | All ceramic capacitors of 5000pF or less in value are ATC type 100 or equivalent. |        | $25\Omega$ , 0.062* O.D. semi rigid co-ax., with L = 28 mm, I = 11 mm (see Figure 3)                      |

| Note 2:  | The Table on Page 1 shows the effect of operating with C9p only or C9s only.      | T2     | 4:1 impedance ratio (output transformer) $25\Omega$ , 0.090 $^{\circ}$ O.D. semi rigid co-ax., with       |

| R1       | 1KΩ 1/2W                                                                          |        | L = 19 mm, I = 9 mm (see Figure 3)                                                                        |

| R2       | 1.5KΩ 1/2W                                                                        |        | (T1 transformer must be loaded with ferrite toroids of suitable dimensions and μi of 35-40.               |

| R3       | 1.5KΩ 2W                                                                          |        | or other type ferrite cores, such as Fair-Rite                                                            |

| R4       | 1Κ $\Omega$ Trimmer Potentiometer                                                 |        | Products Corporation E and I types 9467012002 and 9367021002 respectively.)                               |

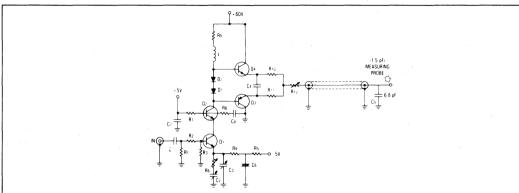

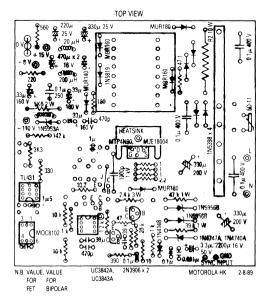

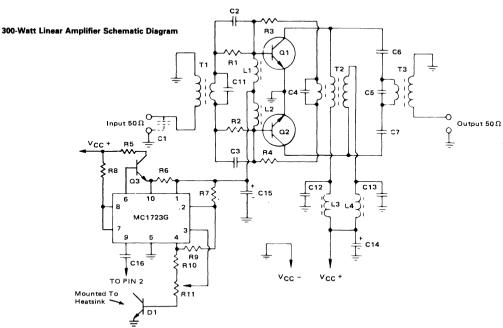

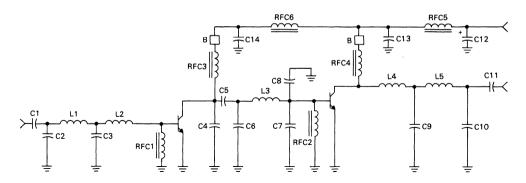

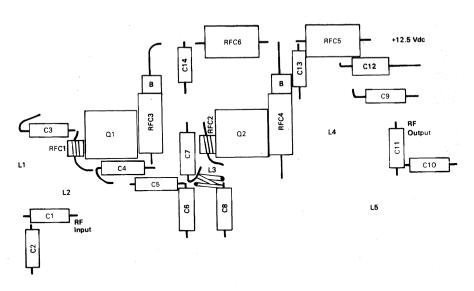

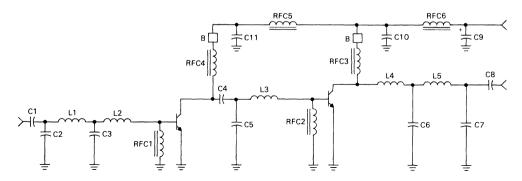

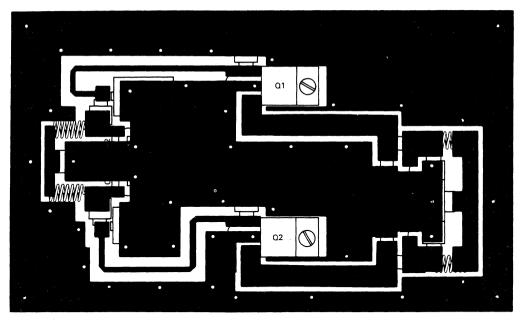

Figure 2. 300 W, 88-108 MHz amplifier schematic and parts list

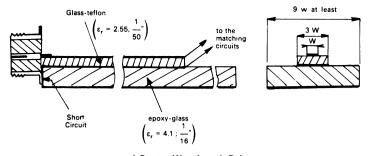

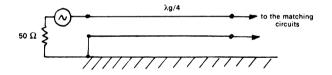

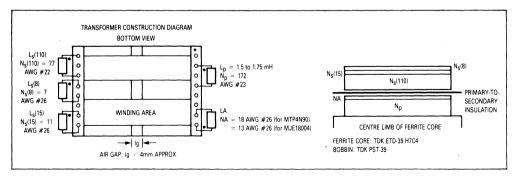

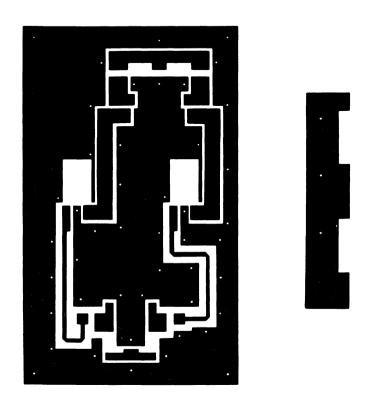

Figure 3. Constructional details of transformers

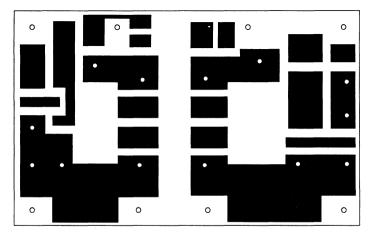

Epoxy glass 1/16"

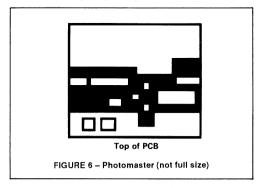

Figure 4. Printed Circuit Board (not full size)

#### "FLOF" Teletext using M6805 Microcontrollers

By Peter Topping MCU Applications Motorola Ltd. East Kilbride

#### 1. INTRODUCTION

The "T" members of the MC68HC05 family of MCUs provide a convenient and cost effective method of adding on-screen-display (OSD) to TVs and VCRs. As well as the 64-character OSD capability, they include 8 Kbytes of ROM (adequate for Teletext, frequency-synthesis, stereo and OSD), 320 bytes of RAM, a 16-bit timer and 8 pulse-width-modulated D/A converters. The MC68HC05T7 also includes IIC hardware and, by using a 56-pin package, 4 ports of I/O independent of the OSD, serial and D/A outputs. It is thus suitable for large full-feature chassis. The MC68HC05T1 is in the middle of the price/performance range and includes most of the features of the MC68HC05T7 but in a 40-pin package. This is achieved by sharing I/O with the other pin functions (SPI, OSD, D/A). Even if all these features are used, there is sufficient I/O for most applications.

The MC68HC05T2 is a 16K upgrade of the MC68HC05T1 and the MC68HC05T3 a 24K version with increased RAM (512 bytes) and enhanced OSD (112 characters and 2 rows of OSD buffer). The low cost MC68HC05T4 has 5 Kbytes of ROM and 96 bytes of RAM making it suitable in simpler (eg mono, non-Teletext) applications. The T4 and T7 also include a 14-bit D/A converter to facilitate voltage synthesis tuning. There are EPROM (and OTP) versions of the T3 (including T1 and T2 emulation), T4 and T7.

This application note describes an example of Teletext control software written for the MC68HC05T7 which directly controls Teletext chips of the type 5243. Spanish FLOF Teletext (level 1.5) is handled using packet X/26. If no CCT teletext chip is present on the IIC bus (as indicated by the lack of an acknowledge), all Teletext functions are disabled in software. About 3Kbytes of ROM are used allowing the code to fit into the 7.9K bytes available in an MC68HC05T7 along with tuning, OSD and stereo functions.

The software in the included listing has been written for the MC68HC05T7 but could, with a little modification, be implemented on other M6805 microcontrollers. A microcontroller without IIC hardware can be used as long as additional software is included to facilitate the IIC bus using I/O pins. An example of IIC master I/O driven software can be found in application note AN446.

#### 2. "FLOF" TELETEXT FEATURES

Full Level One Feature (FLOF) Teletext utilises "ghost" packets to provide features in addition to those available with the original CCT Teletext. The primary enhancement is the provision of a menu with a choice of four linked pages selectable by the user with a single press of one of four coloured buttons on the remote control. The menu itself is sent in the ghost page using packet 24 while the linked page numbers are contained in packet 27. In addition to linked pages, packets 26 and 30 are used. Packet 26 allows for the substitution of selected characters in the display by special characters specific to a particular country. This example application includes the Spanish implementation of packet 26. The broadcast service data packet (8/30) is used to get the initial (index) page for each channel and to display station identification information.

#### "Ghost" packets handled

#### X/24:

The FLOF menu information contained in this page extension packet is transferred by the microcomputer to row 24 of the display chapter. When links are disabled because there is no packet 27 (destination code 0) or when bit 4 of byte 43 is 0, row 24 is blank.

#### X/26:

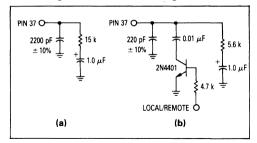

Optional handling of modes 1xxxx, 01111 and 00010 in accordance with the Spanish Teletext specification. All the additional characters which are available in the 5243 CCT chip are handled. The feature can be disabled with a hardware link on an I/O pin (see figure 1) so that the software can be used at level 1.0 in non-Spanish countries also using packet 26.

#### X/27:

This packet contains the linked page numbers for the red, green yellow, blue and index (black) keys. Bit 4 on the link control byte (byte 43) is used to determine if these links are enabled (1) or disabled (0). When enabled, the Spanish specification requires that bits 1, 2 and 3 be used to enable the green, yellow and blue links respectively. This use of these bits is not defined in the World Teletext Specification. For this reason their use is selectable by a hardware link (see figure 1). If these bits are not used, all links (if enabled by bit 4) will be taken from packet 27-but will be automatically disabled if the broadcast links are default (FF3F7F) or invalid.

#### 8/30:

The broadcast service packet is used to supply the index page number on exit from standby and (if teletext is not stopped) after a channel change. Bytes 10-30 of this packet are displayed for 5 seconds on exit from standby and (if teletext is not stopped) after a channel change.

#### 3. IMPLEMENTATION

The software listing is in two parts. The first part contains the "idle" loop and IIC routines from the main TV control part of the MC68HC05T7 application. The idle loop controls the timing of everything performed by the microprocessor, scans the local keyboard, checks whether or not an IR command has been received, etc. It also monitors the relevant flags in the Teletext chip and performs the tasks (eg fetching linked pages) which have to be performed independently of requests for the user.

The second and main listing is the Teletext module itself. It contains all the subroutines required to carry out automatic and user requested Teletext activity. Both modules use the same RAM allocation file (RAMT8.S05) which is included in the listing of the Teletext module. This listing also includes a symbol cross-reference table.

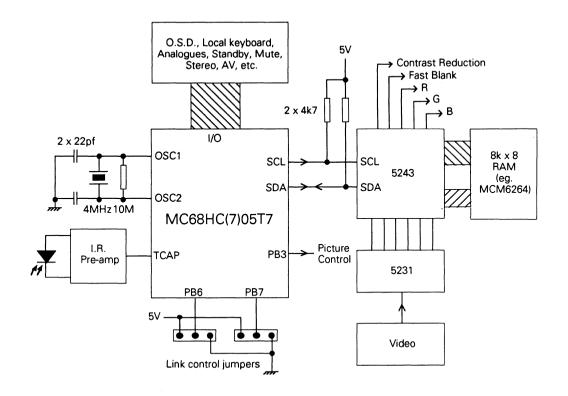

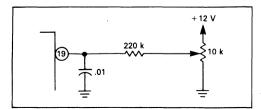

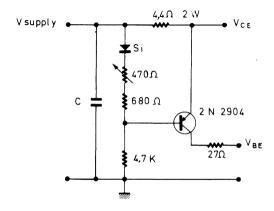

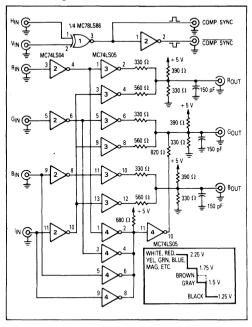

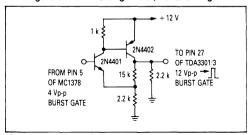

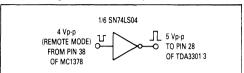

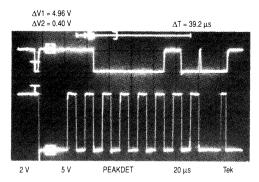

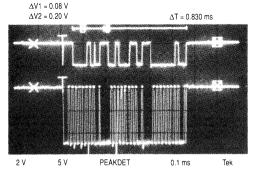

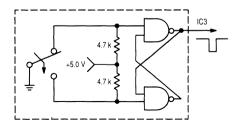

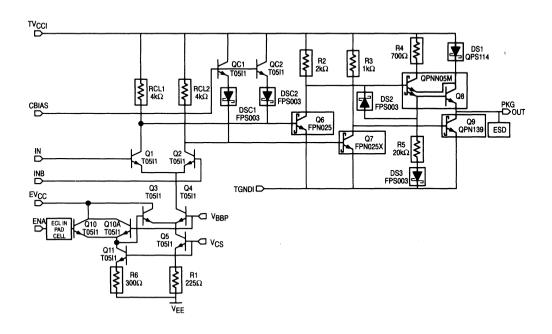

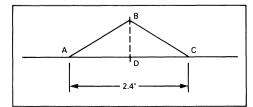

Figure 1 shows a simplified circuit diagram of the application. Most of the MC68HC05T7's I/O is used for purposes other that Teletext and is not shown in detail. Communication with the 5243 Teletext chip is via an IIC bus in which the T7 is always the master. The function of the three I/O pins used for Teletext is described under "Ghost packets handled" and "Inputs and Outputs".

A version of this Teletext software has been implemented on an MC68HC05C4 for use in a TV where the other control functions were handled by a separate microcontroller. The signal from the IR pre-amp was fed into the C4 which used Teletext commands to control a 5243 via a software IIC bus. Non-Teletext commands were regenerated by the C4 and sent to the other microcontroller. This arrangement allows Teletext to be added to a chassis which was originally designed without considering Teletext.

Figure 1. MC68HC(7)05T7 - Teletext application circuit

#### 4. IDLE LOOP

In the example application the idle loop code is in the main TV control software module rather than in the teletext module. Listing 1 shows the relevant parts of this module. The loop time is 12.8mS and it is at this rate that the timing counters used by Teletext (CNT1 and CNT4) are incremented. The standby condition is checked first; if the TV set is in standby then there is no IIC activity and hence no reading from, or writing to, the 5243. If the TV has just exited from standby, as indicated by the flag 3,STAT2, then Teletext is initialised using the sub-routine RESTRT. This sub-routine writes to the 5243's control and mode registers (R5, R6 and R7) and checks that the IIC acknowledge is present. If there was no acknowledge, as indicated by flag 6,STAT7, then no further Teletext activity is attempted.

If an acknowledge is present, Teletext polling goes ahead, although it is suspended if there is a mute or time display. A mute indicates that the channel has just been changed, or no channel is tuned. During time display, all other Teletext activity is suspended. Re-initialisation using sub-routine START2 is performed if flag 7,STAT5 is set by a change of the tuned frequency.

Counter CNT4 is used to delay the transfer of packets 24 (page extension – FLOF menu), 27 (links), 26 (enhanced display characters) and the control bits from row 25 (display page) after the initial arrival of a page. When row 24 is read the 5243 FOUND flag is set to indicate that the arrival has been acted upon. If UPDATE is on then an update indicator appears if the update control bit (C9) is set or if the sub-page has changed or if it is the first arrival of the page. The update display is performed by the sub-routine ARRVD which clears the transient flags and enables the required display, i.e. page no. in normal mode and the whole of row 0 in sub-page mode. Any boxed information (eg sub-titles or newsflash) in the current page is also displayed. The last Teletext function performed by the idle loop is the checking of the FOUND flag in the 5243. This is accessed via the IIC bus; it is on the last (not displayed) row of the display page along with the current page and sup-page numbers and the control bits.

If there is a current Teletext transient (time, row 0 box or packet 8/30), the transient control branch from the idle loop is executed. This routine checks to see if it is time to end the transient. If it is, the subroutine OSDLE is executed. It resets transients for both the OSD generated by the MC68HC05T7 and Teletext. The sub-routine RSTMD2 performs this function for Teletext. It is called from within the sub-routine OSDLE (not listed).

#### 5. REMOTE CONTROL FUNCTIONS

TV/TXT

Togale between TV & Teletext mode.

0-9

Number keys for entry of page and sub-page numbers

Red, Green, Yellow, Blue

Linked page access keys. The decoder stores four pages of text. These are the display page and the three pages corresponding to the red, green and yellow links. The blue linked page is not acquired in advance. In the absence of FLOF data or if the links are disabled by the control bit in packet 27, the red key is page+1 and the green key page-1. Under these circumstances the requested page and the next three pages are acquired.

PC+/-

These keys always select page + 1/page-1 regardless of the availability of FLOF information. As with the red, green and yellow keys, the page is displayed immediately if it is already in RAM.

INDEX

This key operates as an additional link with the difference that if the link is invalid the initial page from packet 8/30 is selected.

SUB-PAGE/TIME

Text mode: Enter sub-page mode, (max. 3979). TV mode: Display time in top-right-hand corner for 5 seconds. Pressing this key during a station identification display (packet 8/30 bytes 10-30) can be used to extend this display beyond the five seconds it appears for, after a channel change.

STOP

Halt acquisition, "STOP" is displayed instead of page number. Press again to restart. If acquisition has been stopped by partially entering a new page number then this key can be used to return to the original page.

#### MIX/NO-MIX

Toggle between Teletext and mixed display. Use of this key causes the display of the top status row for 5 seconds if it is not being displayed because the current page is a newsflash or a sub-title. 5243 contrast reduction is enabled in mixed mode.

#### FULL/TOP/BOT

Selects one of the three display formats, normal, too half enlarged, bottom half enlarged.

#### REVEAL

Reveal hidden text, toggle action.

#### UPDATE

Return to picture until a new version of the requested page arrives. When it arrives, its page no. is displayed in the top-right-hand corner, the key operates in both TV and Teletext mode, set is put into TV mode. Any boxed information (alarm clock, newsflash or sub-title) will be displayed. In sub-page mode the complete header is displayed so that both page & sub-page numbers can be seen. Cancel update by entering Teletext mode and then going back to TV mode by pressing the TV/Text key twice.

#### 6. TELETEXT SUBROUTINES

#### 6a. Subroutines: TVTX, UPDATE, DIGITO and GETIT

The Teletext module (listing 2) comprises various sub-routines which are used both by the idle loop and to perform any Teletext actions initiated by commands from the IR remote control. They are described in the order in which they appear in the listing.

TVTX is executed when the TV/TEXT button is pressed. Its function is to toggle between TV mode and Teletext mode. The flag 0,STAT indicates the current mode. This flag routes the microprocessor to execute either TXTOFF or TXTON according to the current mode. TXTON checks that Teletext hardware is present and does nothing if there has been no IIC acknowledge. If, however, a 5243 is present in the TV, it clears all transients (OSDLE) and sets up the Teletext mode. It initialises the control registers (R5 and R6) to display text and background both in and out of boxes. For newsflashes the set-up is text and background within boxes and picture outside. TXTOFF also resets transients but forces TV mode and sync. Polling and updating continue as a background activity.

When the UPDATE key is pressed the update flag 4,STAT2 is set and TXTOFF executed so the TV is forced to TV mode. If there is a current transient hold (eg time), the hold is cleared before TXTOFF is executed.

The number entry sub-routine DIGIT0 branches to DIGITS in sub-page mode but otherwise accepts any number key as a page number input. Three digits are required, the pointer PDP holding the current position (0, 1 or 2 for hundreds, tens or units). During entry the flag 2,STAT is set to stop Teletext activity. The numbers have to be written to the top-left-hand corner of the display page as well as saved in RAM. Once all three digits have been entered the page is requested and page acquisition restarted.

The code at label GETIT makes this request after first checking whether or not the selected page has already been requested (it could be the current display page or an already requested linked page). If it has, then a switch is made to the chapter associated with the appropriate acquisition circuit and no new request is generated. If not, the new request is made and the FOUND flag set.

#### 6b. Subroutines: Colours, INDEX, NPAGE and PPAGE

The four colour keys (Red, Green, Yellow and Blue) are primarily intended for selecting Teletext linked pages. When pressed the chapter which corresponds to the appropriate acquisition circuit is selected for display. If links are disabled (by the link control bit or because there is no packet 27), then the RED and GREEN keys select current page +1 and-1 respectively. This choice is taken according to the state of flag 3,STAT3 which reflects the condition of the link control bit in packet 27. The code executed by RED, if links are not in use, is the same as that executed by the "+" function (NPAGE) which always selects the next page. Similarly the alternative GREEN function (PPAGE) is the same as for the "-" key. The YELLOW and BLUE keys do nothing under these circumstances. In Spanish Teletext the GREEN, YELLOW and BLUE links can be individually inhibited, but the RED link is only inhibited if all links are off.

The chapter associated with the selected page is displayed immediately if it has already been requested. This will normally be the case if a linked page (red, green or yellow) has been selected. The code at label LPT is executed if the page has already been requested. If not, a jump to CLRPD is performed. CLRPD is a label within DIGITO; the code at CLRPD requests a new page just as if the page number had been entered manually. If the required acquisition circuit is the one already current, then the "unstop" code is executed. This causes the green page-being-looked-for header to roll as though the page number had just been entered. This means that something can be seen to happen in the case where the linked page differs only from the current page in its sub-page number. Linked sub-pages are not fully supported in this implementation as they are rarely used by broadcasters and would significantly increase the size of the software. When the chapter is changed the Teletext PBLF (page being looked for) flag is checked. If it is low the FOUND flag is cleared. This forces the fetching of the links associated with the new display page. If the page is not already in, this will automatically happen when it arrives so the FOUND flag does not need to be cleared.

The BLUE (or cyan) key is different in that its page will not normally be immediately available (the four pages: display, red, green and yellow occupy the four acquisition circuits and RAM chapters).

The INDEX (or black link) function is similar to BLUE except that if its link is not valid it defaults to the initial (index) page number supplied by packet 8/30 (see sub-routine GIP).

#### 6c. Subroutines: LINK, GLP1, GLP2, SRCH, CHCK1 and NOTOKx

The sub-routine LINK allocates the three linked pages (RED, YELLOW and GREEN) to the three free acquisition circuits (not in use by the display page). To do this it checks the page numbers in turn to see if they have already been requested. If so they are left in their current acquisition circuit. If they have not already been requested the page number is put into a LIFO. Only 0-9 are regarded as acceptable digits for page numbers; this is consistent with the Spanish specification although the additional HEX numbers (A-F) may be used experimentally or by Teletext page generators. Within this first loop the sub-routine GLP1 is used to get the linked page numbers from packet 27, perform a decode of the Hamming encoded data and calculate the new magazine number (page hundreds) if different from that of the display page. GLP1 uses sub-routine SRCH to check if the page has already been requested. If there are no links, or if links are disabled, then displayed page +1, +2 and +3 are requested.

The second loop in LINK allocates new page numbers to the remaining unused acquisition circuits. It uses GLP2 to clear the relevant chapters in the Teletext memory and make the new requests. Subroutine CHCK1 is used to check whether or not an acquisition circuit is in use before it is loaded with a new page number from the LIFO.

This method of organising new page requests prevents unnecessary requests being made for pages already requested. This is particularly important when links are disabled and pages are being requested using the "+" or "-" functions. Under these circumstances when the page number is incremented (or decremented) only one new page has to be requested (new display page+3), while page, page+1 and page+2 do not need to change and can be left in their current acquisition circuits.

NOTOK3 and NOTOK2 handle the RED and GREEN functions when links are disabled. They are disabled if the link control bit (packet 27 bit 3, byte 43) is zero or if there is no packet 27. These subroutines respectively increment and decrement the current page number (units and tens). The current magazine number (page hundreds) is not affected.

#### 6d. Subroutines: ROW24, W2B, R2B, GCYI, CLINK and DECODE

ROW24 is used to transfer ghost row 20 (packet 24) into the display chapter. This has to be done via the IIC bus. The loop reads two bytes via the IIC (sub-routine R2B) bus from the ghost page and writes it to the display page (sub-routine W2B). The FOUND flag is then set to indicate that the arrival of the page has been recognised and acted upon. This sub-routine is only called by the idle loop and is used along with the other sub-routines which get information from the ghost page (CLINK, LINK and GET25).

R2B and W2B use IIC routines READ and SEND which are outwith the Teletext module. These subroutines will differ according to the microprocessor in use. An MC68HC05C8 implementation would need to use I/O lines (see reference for suitable software) while the MC68HC05T7 can use its IIC hardware. The routines used in this example are included in the listing extract from the TV control software module (listing 1).

The sub-routine GCYI is used by LINK to store the data associated with the BLUE an INDEX links. As explained above, these pages will not be acquired in advance, the page number only being sent to an acquisition circuit if requested by an IR command.

CLINK fetches the link control byte from packet 27 if the destination code is OK and, after decoding the Hamming encoded data, transfers the bits to STAT3.

The Hamming decode sub-routine DECODE corrects for single bit errors. This is done with in-line code using the table HAM (at the end of listing 2) as this uses less ROM than an algorithmic method.

#### 6e. Subroutines: MIX, TRANx, TXTx, HOLD, and NOHOLD

The mixed display capability of the Teletext chip (5243) is toggled using an IR key which calls the sub-routine MIX. When mixed mode is entered, interlaced broadcast sync. (312/313) is selected because the non-interlaced sync. used for teletext is not suitable if a TV picture is present on the screen. This is set up via the 5243 mode register R1. The control registers R5 and R6 are updated to provide the mixed display.

When returning to a non-mixed display, the code at NOMIX is used to re-configure the control registers and to set up a Teletext only 312/312 non-interlaced sync. This sync. reduces adjacent line flicker in a pure Teletext display.

The subroutine TRAN2 sets up a transient which retains a black background on the top row so that the page number, time etc. can be seen clearly. This type of transient is also started if the page number or sub-page number is being entered in mixed mode. Sub-routines TRAN1, TRAN2 and TRAN3 are used to initialise the various transient displays. These displays are cancelled as discussed above by actions taken within the idle loop controlled by the free-running timer within the MC68HC05T7.

The TXTx sub-routines are used in conjunction with the IIC SEND routine to write to various sub-sets of the registers within the 5243.

If the Teletext STOP function is requested by an IR command the routine HOLD is executed. This is a toggled function when requested in this way. HOLD displays the word "STOP" in place of the page number and stops the display acquisition circuit by clearing the 5243 HOLD flag accessed via its page request register R3.

NOHOLD is executed to restart the display acquisition circuit. It returns the page number to the top-left-hand corner. If a new page number has been partially entered, a press of STOP (executing an UNHOLD) will allow a return to the most recent page request. This takes only a single press as the start of the entry of a new page number cause a HOLD. The completion of a page number entry (3 digits) causes a NOHOLD.

#### 6f. Subroutines: REVEAL, EXPTB and TIME

The REVEAL function causes any hidden display information to appear. It is controlled by a bit in the display mode register (R7). The software example leaves any revealed information permanently displayed. If, however, it is required that such information disappear when the page is updated (this may be better for a quiz page), then the two commented out lines (80 and 81) in the idle loop should be enabled.

The display expand facility is controlled by another two bits in R7. The EXPTB sub-routine cycles through normal, top-half double height and bottom-half double height.

The example application uses a single IR key (subroutine TIME) for both the display of the Teletext clock and the entry into sub-page mode. IF the set is in TV mode then the time is displayed for 5 seconds. If the TV is in Text mode then sub-page mode is selected. Sub-page number entry is described in the following section. When the Teletext clock is requested it appears (boxed) at the top-right-hand corner. It is removed by the idle loop 5 seconds after the last press of the time button. When the time is being displayed all other Teletext activity is stopped using UCHOLD.

#### 6g. Subroutines: DIGITS, SUBPG, GET25 and GET26

DIGITS is the sub-page version of DIGIT0 and uses similar code. More checks on the input data are required as the four digits of the sub-page number have different maximum values. These maximums are 3 for thousands, 7 for the tens and 9 for the hundreds and units. These values reflect the sub-page number's original use as a time (24hr format). For tens and thousands a keyed 8 becomes a 0 and a 9 becomes a 1; for thousands only 4, 5, 6 and 7 become 0, 1, 2 and 3 respectively.

The code at the label SETIT is the sub-page equivalent of GETIT, described above. It requests the new sub-page and sets the FOUND flag.

The sub-routine SUBPG is called when the TIME (or clock) key is pressed (TV in Teletext mode). It toggles between normal mode and sub-page mode. When sub-page mode is entered the page number display (P—) is replaced with \*\*\*\* to indicate the mode change and to prompt for the entry of a sub-page number. Once all four digits have been entered the new sub-page is requested by SETIT. The code at the label RSTR is used to exit from this mode back to the normal (page number) mode, restoring the page number display to the top-left-hand corner.

GET25 is used by the idle loop to get the information stored in row 25 of the display chapter. This row is not displayed but contains various information used by the control microprocessor. The current page number, magazine number, sub-page number, Teletext control bits and the FOUND and PBLF flags are available. GET25 gets the required information and stores it in the RAM of the MC68HC05T7.

At the end of this sub-routine the I/O line 7,portB is checked. If it is low, packet 26 is handled. If it is high, this packet is disabled. This would be required if this application were to be used in a country other than Spain which used packet 26. It would require to be switched off as the enhanced display feature uses different characters depending on the country. In countries which do not use packet 26 (eg the UK) it does not matter whether or not packet 26 is enabled.

If packet 26 is enabled, GET26 processes all packet 26 data present in the ghost page. The tables G2TAB, G3TAB and CTAB contain the characters used to replace the character at the display location defined by each packet.

#### 6h. Subroutines: GIP. R24T and SR24T

The sub-routine GIP gets the initial (index) page from packet 8/30. It will be doing this as the set is brought out of standby or just after a channel change. It may thus initially get a poor signal (or there may be no Teletext) so it tries repeatedly until it finds a valid packet 8/30 format 1. If this is not found after 96 tries it gives up and sets the flag 6,STAT2 to indicate that there is no packet 8/30 (or no Teletext). In this circumstance it defaults to an index page number of 100.

R24T transfers bytes 10-30 of the broadcasting service data packet (8/30) into the display chapter. It is called once a second for five seconds after power-on or a channel change. The data is transferred to row 0 of the display page which can be displayed either at the bottom or, as in this example, the top of the screen. This transient display is setup using the sub-routine SR24T if Teletext is present. If the flag 6,STAT2 has been set by GIP as described above then SR24T does nothing. The transient display is terminated by code executed at the appropriate time from within the idle loop.

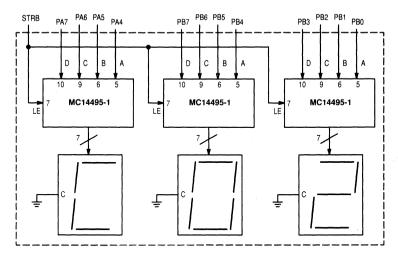

#### 7. INPUT AND OUTPUTS

Apart from the IIC bus, only three pins on the controlling microprocessor are relevant to Teletext. Two inputs select the usage of packets 26 and 27 and one output can be used to control any hardware which requires to be changed according to whether or not there is a TV picture currently being displayed. In many applications some or all of these functions will not be required and could be eliminated from the software thus freeing up the pins for other uses.

PB3)

This pin is active (high) during a pure (no-mixed, no-boxed) teletext display, otherwise it is low.

PB6)

When this pin is low, Spanish use of link control bits 1, 2 and 3 is enabled. When it is high, these bits are ignored.

PB7)

Packet 26 control. When low, packet 26 is enabled and handles all the Spanish alternate characters which are available in the 5243. When PB7 is high, packet 26 is ignored.

#### 8. REFERENCES

Application note AN446, MCM2814 Gang-programmer using an MC68HC05B6.

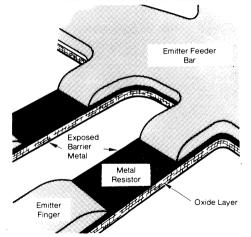

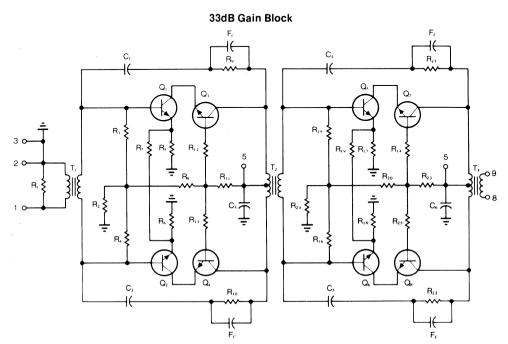

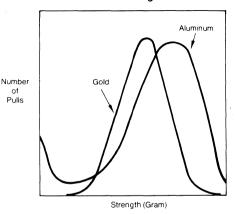

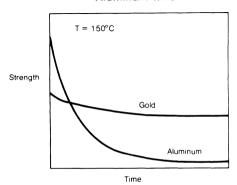

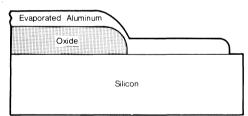

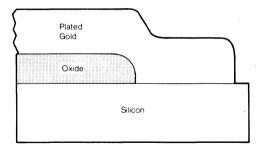

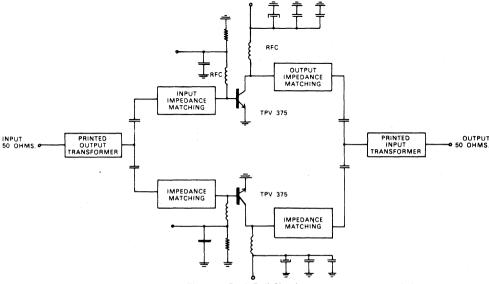

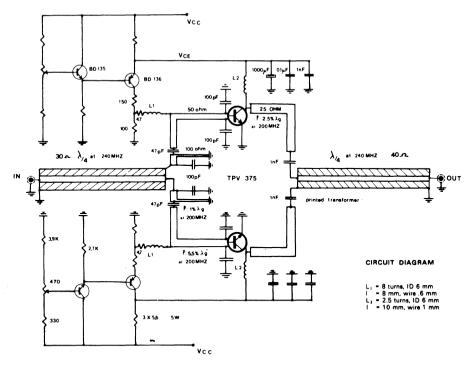

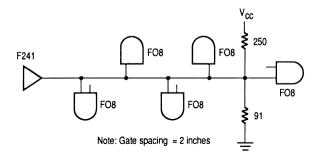

#### LISTING 1